专利摘要

本发明公开了一种格雷码双边沿触发计数器,模N的计数器由N+1组触发器组合构成,每组触发器主要由两个受控条件相异的锁存器和附加逻辑电路构成;每组触发器包括一个正向输出和一个反向输出,反向输出提前正向输出半个周期,第一组触发器输出计数器的CNT[0]位,第N组触发器输出计数器的第CNT[N-1]位,第N+1组触发器的输出作为第一组触发器的输入;第二组触发器的输入由第一组触发器的反向输出与CNT[N+1]经或非门后得到;第M级的输入由CNT[0]的反向输出和CNT[M-2:1]的正向输出以及第N+1级的反向输出经与非门后,将与非门的输出与M-1级触发器组合的反向输出经或非门后得到。

说明书

技术领域

本发明涉及一种逻辑电路中的计数器,尤其涉及一种格雷码计数器。

背景技术

传统的二进制计数器在工程应用中存在缺陷,在某些领域,如高稳定性的工程控制中难以保证计数的稳定性和唯一性,因为二进制计数器的每一次计数伴随着多位的翻转,在翻转过程中可能存在多种过渡状态,这些过渡状态会增加了计数结果的不确定性,如从011到100,三个比特都发生了翻转,如果每个比特变化的时间有偏差,就会出现如000,101,110等过渡态,这些过渡态在工业控制中会导致严重的工程事故,用在交通灯上则导致交通灯变化的不确定。

而格雷码计数器成功的解决了二进制计数器的这一缺陷,格雷码计数器的计数原理是每次计数只有一个比特在翻转,保证了计数结果的唯一性,消除了过渡态,以下是3位格雷码计数器和二进制计数器的计数码字比较。

传统的格雷码计数器有两种实现方式:一种是通过将二进制计数的码字作以下操作得到,对于模N的计数器:CNT[N-1:0],

gray_cnt[N-1]=bin_cnt[N-1]不变,

gray_cnt[N-2]=bin_cnt[N-1]^bin_cnt[N-2],

gray_cnt[M]=bin_cnt[M+1]^bin_cnt[M],

gray_cnt[0]=bin_cnt[1]^bin_cnt[0];

另一种是由N+1个触发器构成的N位格雷码计数器,第0位计数器在每个计数时钟沿反向,第一位触发器CNT[1],当第0位触发器CNT[0]为1时,第一位触发器CNT[1]在计数时钟沿反向,第M位触发器CNT[M],M为1<M<N的自然数,当第M-1位触发器CNT[M-1]为1,第0位触发器CNT[0]到第M-2位触发器CNT[M-2]全为0,第M位触发器CNT[M]在计数时钟沿反向,第N位触发器CNT[N],当第0位触发器CNT[0]到第N-2位触发器CNT[N-2]全为0,第N位触发器CNT[N]在计数时钟沿反向。将第N位触发器CNT[N]到第一位触发器CNT[1]输出即得到N位格雷码计数器的输出。

在以上两种方式中,第一种由于二进制计数存在过渡态,所以转换后的格雷码也存在过渡态,第二种格雷码计数器可以得到不存在过渡态的格雷码计数结果,但只能针对单一时钟沿进行计数,增加了计数周期的长度。

发明内容

针对上述现有技术,本发明要解决的技术问题是提供一种在计数时钟上升沿和下降沿都会触发计数的格雷码双边沿触发计数器。

为了解决上述技术问题,本发明采用如下技术方案:一种格雷码双边沿触发计数器,模N的计数器由N+1组触发器组合构成,其中,每组触发器包括两个受控条件相异的锁存器;

所述锁存器包括正向输入端D和反向输入端DB、正向输出端Q和反向输出端QB,

第一组触发器为下降沿触发器,其中,第一锁存器的正向输出端Q和反向输出端QB分别连接第二锁存器的正向输入端D和反向输入端DB,第二锁存器的反向输出端QB与时钟信号经过异或门连接第一锁存器的反向输入端,异或门信号还经过非门连接第一锁存器的正向输入端;

其中第一锁存器的反向输出端QB经过一非门后作为触发器的反向输出端INV,第二锁存器的正向输出端Q作为触发器的正向输出端OUT;

第二组至第N+1组触发器为上升沿触发器,其中,第二锁存器的正向输出端Q和反向输出端QB分别连接第一锁存器的正向输入端D和反向输入端DB,第一锁存器的反向输出端QB与时钟信号经过异或门连接第二锁存器的反向输入端,异或门信号还经过非门连接第二锁存器的正向输入端;

其中第二锁存器的反向输出端QB经过一非门后作为触发器的反向输出端INV,第一锁存器的正向输出端Q作为触发器的正向输出端OUT;

每组触发器的反向输出和正向输出端分别处于触发器的两个时钟边沿,且反向输出提前正向输出半个周期;

第一组触发器输出计数器的CNT[0]位,第N组触发器输出计数器的第CNT[N-1]位,第N+1组触发器的输出作为第一组触发器的输入;

第二组触发器的输入由第一组触发器的反向输出与CNT[N+1]经或非门后得到;

第M级的输入由CNT[0]的反向输出和CNT[M-2:1]的正向输出以及第N+1级的反向输出经与非门后,将与非门的输出与M-1级触发器组合的反向输出经或非门后得到,其中M为2<=M<=N+1的自然数。

进一步地,所述第一锁存器在输入时钟信号为低电平时读取数据,高电平时进行数据锁存;第二锁存器在输入时钟信号为高电平时读取数据,低电平时进行数据锁存,且第一锁存器LATCH1和第二锁存器LACHT2的CLR和RST端都为低电平有效。

与现有技术相比,本发明具有以下有益效果:本发明中提出的设计方案结合上升沿触发器和下降沿触发器的特点,设计了一种在计数时钟上升沿和下降沿都会触发计数的格雷码计数器,在每个时钟沿计数器码字只有一个比特发生翻转,满足格雷码计数器的计数原则,同时有效的提高了计数效率,在相同的计数模下,将计数周期缩短了一半,在高速数据转换领域具有很高的应用价值。

附图说明

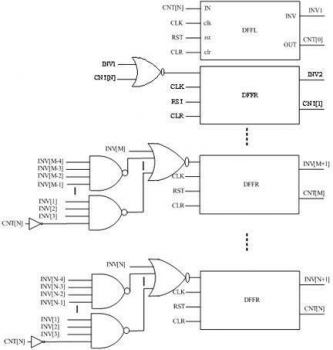

图1为两个锁存器构成的计数器基本触发器组合结构逻辑图;

图2为CNT[0]的逻辑电路图;

图3为CNT[1]的逻辑电路图;

图4为CNT[M]的逻辑电路图;

图5为CNT[N]的逻辑电路图;

图6为本发明的总体电路图;

图7计数器变化时序图。

具体实施方式

下面将结合附图及具体实施方式对本发明作进一步的描述。

参见图1-图6,首先,构造第一锁存器LATCH1和第二锁存器LACHT2。其中第一锁存器LATCH1在输入时钟为低电平时读取数据,高电平时进行数据锁存;第二锁存器LATCH2在输入时钟为高电平时读取数据,低电平时进行数据锁存,且第一锁存器LATCH1和第二锁存器LACHT2的CLR和RST端都为低电平有效。当CLR和RST端都为高电平时第一锁存器LATCH1和第二锁存器LACHT2进入正常工作状态,CLK为低时,第一锁存器LATCH1读取D、DB端的信号(D、DB互为反相信号)并在Q1、Q1B端输出,而第二锁存器LACHT2的输出端保持原来的状态不变;当CLK变为高电平后,第一锁存器LATCH1的输出端保持不变,第二锁存器LATCH2读取第一锁存器LATCH1的输出信号,并在Q2、Q2B端输出,且在CLK变为高电平时Q2、Q2B保持不变,第一锁存器LATCH1读取下一个信号。

再将两个锁存器组合成图1所示的两种触发器组合,(a)为下降沿输出触发器组合DFFL,(b)为上升沿输出触发器组合DFFR。根据对计数器输出的需求,设置每个计数位的输出是在时钟的上升沿或下降沿。在本例中,CNT[0]在时钟的下降沿输出,即CNT[0]作为计数器的最低位将在每个时钟的下降沿电平翻转,CNT[1]-CNT[N-1]在时钟的上升沿电平翻转,因此,选择DFFL作为第一级的计数输出,DFFR作为第二级至第N级的输出。

作为计数器的最低位输出,CNT[0]的输入来自CNT[N]输出,CNT[N]在计数开始前为高电平,计数开始后CNT[N]被复位信号复位至低电平,反向后作为CNT[0]的输入,从图1中(1)DFFL得出,当IN为高时,QB端将在半个时钟周期后被置高,导致CNT[0]将在每个时钟下降沿翻转。

在每一个触发器组合的输出端,都有一个正向输出和一个反向输出,其中,反向输出和正向输出分别处于触发器的两个时钟边沿,且反向输出INV提前正向输出半个周期,即对于第一组触发器DFFL反向输出端在时钟上升沿输出,正向输出端在时钟下降沿输出;对于后面的DFFR,反向输出端在时钟下降沿输出,正向输出端在时钟上升沿输出;INV将作为下一级的组合逻辑输入如图2所示,将上一级计数器的输出提前半个周期传递至下一级计数器,使得下一级计数器输出总是上一级计数器输出的二分频且在上一级输出为低时发生电平翻转,保证了在每一个时钟沿只有一位计数器输出发生电平翻转,满足了格雷码计数器的计数变化规律。

在初始状态,第N组触发器组合的CLR被置低,使得CNT[N]置高,计数器处于关闭状态,当计数使能信号到来后,CLR翻转至高电平,CNT[N]被复位位低,计数器开始计数,当计数器处于计数状态时,CLR信号和RST信号都为高电平;在计数过程中,外部复位信号可将RST信号置零,CNT[N]被置高,计数器清零。以3为模的计数器,其输出的变化规律为:每个时钟沿输出有一位发生翻转,变化规律为111 —>110—>100—>101—>001—>000—>010—>011。

本发明的计数结果码字变换如图7所示,CNT[0]在每个时钟的下降沿翻转,CNT[M]是CNT[M-1]的二分频,每个码字在时钟的上升沿或下降沿只有一个比特发生翻转。

以模3的计数器为例,计数器的变化规则如下表。

计数器码字变化对照表

双边沿触发格雷码计数器的基本单元是由上升沿触发器和下降沿触发器构成的触发器组合,第一组触发器输出计数器的CNT[0]位,第N组触发器输出计数器的第CNT[N-1]位,第N+1组触发器的输出作为第一组触发器的输入。每组触发器包括一个上升沿输出信号和一个下降沿输出信号,根据输出需求的不同,可以设置每一位计数器的翻转由D_up还是D_down决定,在本设计中,我们要求CNT[0]的在时钟下降沿翻转,CNT[N-1:1]在时钟的上升沿翻转,因此,CNT[0]由D_down输出,而D_up的输出与CNT[N+1]经或非门后作为第二级触发器组合的输入,从CNT[2]到CNT[N],第M(M为2<=M<=N的自然数)级D_dwon的输入由CNT[0]的D_up输出和M-2:1的D_down输出以及第N+1级的反向输出经与非门后,将与非门的输出与M-1级触发器组合经或非门后得到。CNT[N-1:1]由D_up输出,第N+1组触发器的上升沿输出输入到第一组触发器的输入端。

该计数器每一比特的变化规律为:

CNT[0]在每个时钟上升沿或下降沿沿翻转,CNT[M] (1<=M<=N-1)的输出是在时钟的上升沿对前一位计数输出CNT[M-1]进行二分频。

一种格雷码双边沿触发计数器专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0