专利摘要

本发明公开了一种锁频环,其包括数字环路滤波器、数据采集单元、比较单元、老化校正字生成单元和校正单元。所述数据采集单元采集所述数字环路滤波器输出的数字数据,并对所述数字数据进行权重处理以得到权重数值,并将所述权重数值作为当前权重数值提供给所述比较单元,所述比较单元比较当前权重数值和标准权重数值,并将比较结果提供给所述老化校正字生成单元,所述老化校正字生成单元根据比较结果对当前老化校正字进行调整以生成最新的老化校正字,所述校正单元利用所述最新的老化校正字对所述频率控制字进行校正。在晶体振荡器出现了老化频率漂移时,通过老化补偿反馈回路的漂移补偿,从而可以消除或减小对输出频率的影响。

说明书

技术领域【技术领域】

本发明涉及电子电路设计领域,特别涉及频率合成器和锁频环的补偿技术。

技术背景【背景技术】

晶体振荡器输出的频率都会随着温度的变化而发生漂移,这样基于晶体振荡器输出的频率而生成的各种频率都会随之发生漂移,为了解决这个技术问题,申请号为200810037670.5,公开日为2008年9月24日,公开号为CN101272142A的中国专利申请公开了一种温度频率补偿的频率合成器,图1示出了该专利申请中的所述频率合成器的结构方框图。

如图1所示,所述频率合成器100包括振荡电路101、锁频环107、频率校正单元109、数字温度传感器103、解码逻辑单元105、频率校正查找表111和插值逻辑单元115。所述振荡电路101借助晶体振荡器117生成参考频率信号fR。所述锁频环107基于所述参考频率信号fR和频率校正控制字FCW_new生成期望输出频率fOUT。所述频率校正单元109根据温度频率校正字FCWtmp补偿自动频率控制字FCWAFC以得到频率校正控制字FCW_new,其中:FCW_new=FCWAFC+FCWtmp。所述自动频率控制字FCWAFC包括固定频率控制字FCW和自动频率校正字AFC,所述自动频率控制字FCWAFC可以表达为下式:FCWAFC=FCW+AFC。

预先根据晶体振荡器117的温度频率特征曲线确定各个离散温度点对应的温度频率校正值,并将这些数据存储于频率校正查找表111内,之后根据数字温度传感器103感应到的当前温度值在频率校正查找表111找到合适的温度频率校正字FCWtmp,之后由插值逻辑单元115对所述合适的温度频率校正字FCWtmp进行插值处理以得到当前温度值对应的温度频率校正字FCWtmp,随后利用温度频率校正字FCWtmp对自动频率控制字FCWAFC进行温度频率漂移补偿以得到温度频率校正后的频率校正控制信号FCW_new。这样,就实现了对晶体振荡器的温度频率漂移的补偿。

200810037670.5号专利申请中的温度频率校正属于频率预校正,即由于可以测得晶体振荡器的温度频率漂移曲线,因此可预先配置温度频率校正字对温度频率漂移进行校正。然而,晶体振荡器还会随着老化而产生频率漂移,比如在一电子设备使用初期,其内的晶体振荡器输出的频率在经过上述温度频率校正后会非常准确,但在该电子设备使用了1或2年后,其内的晶体振荡器输出的频率虽经过温度频率校正但仍会发生漂移。

目前来讲,对于晶体振荡器的由于老化而产生频率漂移,还没有非常有效的、合适的解决方案。

发明内容【发明内容】

本部分的目的在于概述本发明的实施例的一些方面以及简要介绍一些较佳实施例。在本部分以及本申请的说明书摘要和发明名称中可能会做些简化或省略以避免使本部分、说明书摘要和发明名称的目的模糊,而这种简化或省略不能用于限制本发明的范围。

本发明要解决的技术问题之一在于提供一种锁频环,其可以补偿由于晶体振荡器的老化而产生的频率漂移。

本发明要解决的技术问题之一在于提供一种频率合成器,其可以补偿由于晶体振荡器的老化而产生的频率漂移。

为了解决上述问题,根据本发明的一个方面,本发明提供了一种锁频环,其包括数字环路滤波器、数据采集单元、比较单元、老化校正字生成单元和校正单元。所述数据采集单元采集所述数字环路滤波器输出的数字数据,并对所述数字数据进行权重处理以得到权重数值,并将所述权重数值作为当前权重数值提供给所述比较单元,所述比较单元比较当前权重数值和标准权重数值,并将比较结果提供给所述老化校正字生成单元,所述老化校正字生成单元根据比较结果对当前老化校正字进行调整以生成最新的老化校正字,所述校正单元利用所述最新的老化校正字对所述频率控制字进行校正。

进一步的,在所述输出频率锁定后,数据采样单元采集数字环路滤波器输出的数字数据,并对所述数字数据进行权重处理得到一个初始权重数值,并将这个初始权重数值提供给所述比较单元作为标准权重数值。

进一步的,为老化校正字生成单元设置的初始老化校正字,在第一次进行老化漂移补偿时,当前老化校正字为初始老化校正字。

进一步的,所述老化校正字生成单元将不断的对所述当前老化校正字进行调整,直到所述当前权重数值收敛于标准权重数值时为止。

进一步的,所述比较单元输出的所述比较结果包括当前权重数值大于标准权重数值和当前权重数值小于标准权重数值,在当前权重数值大于标准权重数值时,所述老化校正字生成单元需要调小所述老化校正字,在当前权重数值小于标准权重数值时,所述老化校正字生成单元需要调大所述老化校正字。

进一步的,所述校正单元根据下式对所述频率校正字进行老化校正或补偿:FCWACW=FCW+ACW,其中FCWACW表示校正后的频率校正字,FCW表示频率校正字,ACW表示老化校正字。

进一步的,其还包括数字相位累加器、数字频率比较器、数字模拟转换器、低通滤波器、压控振荡器和频率数字转换器,其中所述数字相位累加器,接收校正后的频率校正控制字,并基于参考频率信号和校正后的频率校正控制字生成参考频率数据流;所述压控振荡器基于输入电压生成频率信号,所述频率数字转换器提供表示所述压控振荡器输出的频率信号的频率值的数字频率数据流;数字频率比较器,比较所述数字频率数据流和所述参考频率数据流,并输出误差信号;所述数字环路滤波器与数字频率比较器相连接,用于对数字频率比较器输出的误差信号进行滤波;所述数字模拟转换器,与数字环路滤波器相连接,接收数字环路滤波器的输出以生成模拟信号;所述低通滤波器,用于对所述模拟信号进行滤波,滤波后的模拟信号用于控制所述压控振荡器的输入电压。

进一步的,其还包括数字相位累加器、数字频率比较器、数字模拟转换器、增益控制器、数控振荡器和频率数字转换器,其中所述数字相位累加器,接收校正后的频率校正控制字,并基于参考频率信号和校正后的频率校正控制字生成参考频率数据流;所述数控振荡器生成的频率信号,所述频率数字转换器提供表示所述数控振荡器输出的频率信号的频率值的数字频率数据流;数字频率比较器,比较所述数字频率数据流和所述参考频率数据流,并输出误差信号;所述数字环路滤波器与数字频率比较器相连接,用于对数字频率比较器输出的误差信号进行滤波;所述增益控制器,与数字环路滤波器相连接,接收数字环路滤波器的输出以生成用于控制所述数控振荡器的数字控制信号。

根据本发明的一个方面,本发明提供了一种频率合成器,其包括:振荡电路,用来基于晶体振荡器生成参考频率信号;和如上所述的锁频环。

与现有技术相比,本发明在晶体振荡器出现了老化频率漂移时,通过老化补偿反馈回路可以对由于晶体振荡器的老化而引起的频率漂移进行补偿,从而可以消除或减小对输出频率的影响。

关于本发明的其他目的,特征以及优点,下面将结合附图在具体实施方式中详细描述。

附图说明【附图说明】

结合参考附图及接下来的详细描述,本发明将更容易理解,其中同样的附图标记对应同样的结构部件,其中:

图1示出了现有技术中的一种频率合成器的结构方框图;

图2示出了本发明中的频率合成器的一个实施例的结构方框图;

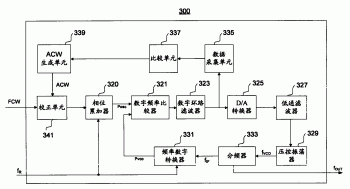

图3示出了本发明中的锁频环的一个实施例的结构方框图;

图4示出了本发明中的锁频环的另一个实施例的结构方框图;

图5示出了本发明中的锁频环的再一个实施例的结构方框图;和

图6示出了本发明中的锁频环的另外一个实施例的结构方框图。

具体实施方式【具体实施方式】

本发明的详细描述主要通过程序、步骤、逻辑块、过程或其他象征性的描述来直接或间接地模拟本发明技术方案的运作。为透彻的理解本发明,在接下来的描述中陈述了很多特定细节。而在没有这些特定细节时,本发明则可能仍可实现。所属领域内的技术人员使用此处的这些描述和陈述向所属领域内的其他技术人员有效的介绍他们的工作本质。换句话说,为避免混淆本发明的目的,由于熟知的方法、程序、成分和电路已经很容易理解,因此它们并未被详细描述。

此处所称的“一个实施例”或“实施例”是指可包含于本发明至少一个实现方式中的特定特征、结构或特性。在本说明书中不同地方出现的“在一个实施例中”并非均指同一个实施例,也不是单独的或选择性的与其他实施例互相排斥的实施例。此外,表示一个或多个实施例的方法、流程图或功能框图中的模块顺序并非固定的指代任何特定顺序,也不构成对本发明的限制。

图2示出了本发明中的频率合成器200的一个实施例的结构方框图。所述频率合成器200包括振荡电路201和锁频环203,所述振荡电路201借助晶体振荡器301生成参考频率信号fR,所述锁频环203基于参考频率信号fR并根据频率控制字(Frequency Control word,简称FCW)产生期望的输出频率fOUT。通过定义合适的频率控制字,用户可以得到期望的输出频率。所述频率控制字可以用二进制序列表示,比如32、16或8位的二进制序列,它可以是经过温度频率校正后的频率控制字,也可以是未经温度频率校正的频率控制字,还可以是经过其他处理的频率控制字。所述锁频环203可以检测输出频率fOUT的由于晶体振荡器301老化而引起的频率漂移,并根据所述频率漂移对频率控制字进行老化校正或补偿,随后利用老化校正后的频率控制字进行锁频。

图3示出了本发明中的锁频环300的一个实施例的结构方框图,所述锁频环300可以用作图2中的锁频环203。所述锁频环300可以根据频率控制字FCW定义的期望输出频率来锁定频率,其包括相位累加器320、数字频率比较器321、数字环路滤波器323、D/A(digital-to-analog)转换器325、低通滤波器327、压控振荡器(voltage-controlled oscillator,简称VCO)329及包括分频器333及频率数字转换器331的反馈回路。

与传统工作在相域的锁相环不同,所述锁频环300工作在频域,所述锁频环300的一个优点在于所述频率比较器321具有高线性度并且可以设计为全数字逻辑电路。所述传统的锁相环通常用模拟电路来实现,这样使它的设计成本增加而且难以实现和数字电路的自由集成。此外,所述模拟锁相环还对工艺、电压和环境的变化很敏感。对于锁频环来说,通过设定FCW值可以产生任何期望的输出频率,频率的精度由FCW的字长和参考频率fR决定。举例来说,参考频率fR为50MHz,FCW的字长为32位,那么频率的精度可达到50MHz/232=0.01Hz。

通过使用高线性度的数字频率比较器321和数字环路滤波器323,锁频环300可以获得低噪声和高精度信号。用在反馈路径中的分频器333可以将压控振荡器329生成的频率信号fVCO分频至中频信号fIF,其中fIF=fVCO/div_n,div_n是分频器133的分频因子。所述频率数字转换器331提供表示其输入信号fIF的频率值的数字频率数据流Pvco。所述频率数字转换器331的作用在于利用参考频率fR对输入信号fIF的时钟周期(比如上升沿或下降沿)进行计数,预定时钟数被标准化为数字频率数据流Pvco,所述数字频率数据流Pvco将会作为数字频率比较器321的一个输入。所述相位累加器320以参考频率fR为基础生成表示输入频率控制字FCW设定频率值的参考频率数据流Posc。

当环路锁定后,数字频率数据流Pvco应当与参考频率数据流Posc相同。所述数字频率比较器321通过比较数字频率数据流Pvco和参考频率数据流Posc产生一个误差信号。随后,所述数字环路滤波器323对所述误差信号进行数字滤波。所述数字环路滤波器323提供环路带宽和锁定调节时间的控制。通过使用所述数字环路滤波器323,可以根据锁频环的需要(比如相位噪声和调节时间)有效控制环路带宽和锁定调节时间。所述数字环路滤波器323的输出被输入至数字模拟转换器325以生成一个模拟信号。所述数字模拟转换器325的模拟输出信号在经过所述低通滤波器327的进一步的低通滤波后用于控制压控振荡器329的输入电压。当环路锁定后,压控振荡器329的输出被锁定于频率控制字FCW设定的期望频率。

然而,晶体振荡器301的老化会引起参考频率fR的漂移,从而会导致数字频率数据流Pvco和参考频率数据流Posc的变化,虽然环路最后仍然会锁定,并且锁定后数字频率数据流Pvco仍然与参考频率数据流Posc相同,但此时压控振荡器329的输出频率已经发生了漂移,这种漂移是无法通过上述环路来调节或校正的。为了校正或补偿由于晶体振荡器301的老化而引起的漂移,所述锁频环300还配置有数据采集单元335、比较单元337、老化校正字(aging correction word,简称ACW)生成单元339和校正单元341,这些单元可以统称为老化补偿反馈回路。

由于数字环路滤波器323输出的数字数据经过数字模拟转换器325及低通滤波器327后就被用作输入压控振荡器329的模拟电压,而在输出频率fOUT锁定后,所述模拟电压应该会较长时间的收敛于一固定值附近,那么相应的,数字环路滤波器323输出的数字数据在较长时间内应该也是收敛的。因此,所述数据采集单元335被设置来采集数字环路滤波器323输出的数字数据,并对所述数字数据进行权重处理得到一权重数值,其中所述权重数值在物理含义上与输入压控振荡器329的模拟电压是直接对应的,也就是说所述权重数值可以直接反映输入压控振荡器329的模拟电压的值。进一步来讲,所述权重数值就可以直接反映压控振荡器329的输出频率的值,换句话来说,如果压控振荡器329的输出频率产生了漂移,那么就会导致所述权重数值发生漂移或变化。

在所述频率合成器或所述锁频环投入应用前或投入市场前,可以对老化补偿反馈回路中的各个单元进行初始化。在一个实施例中,在所述输出频率fOUT锁定后,数据采样单元335采集数字环路滤波器323输出的数字数据,并对所述数字数据进行权重处理得到一个初始权重数值,并将这个初始权重数值提供给所述比较单元337作为标准权重数值。此外,还可以设置老化校正字生成单元339内的初始老化校正字,比如设置所述初始老化校正字为0。

经过初始化后,可以设置每隔预定时间进行一次老化漂移补偿或校正,也可以设置实时进行老化漂移补偿或校正。在进行老化漂移补偿或校正时,所述数据采集单元335采集数字环路滤波器323输出的数字数据,并对所述数字数据进行权重处理以得到一权重数值,并将所述权重数值作为当前权重数值提供给比较单元337。所述比较单元337比较当前权重数值和标准权重数值,并将比较结果提供给所述ACW生成单元339,所述ACW生成单元339根据比较结果对当前ACW进行调整以生成最新的ACW,所述校正单元341利用最新的ACW对所述FCW进行校正或补偿。

随后,所述数据采集单元335继续采集数字环路滤波器323输出的数字数据,并继续对所述数字数据进行权重处理以得到另一权重数值,并将所述另一权重数值作为当前权重数值提供给比较单元337。所述比较单元337继续比较当前权重数值和标准权重数值,并将并将比较结果再次提供给所述ACW生成单元339,所述ACW生成单元339再次根据比较结果对当前ACW进行调整以生成最新的ACW,所述校正单元341利用最新的ACW对所述FCW进行校正或补偿。不断重复上述操作,直到所述当前权重数值收敛于标准权重数值时为止。

老化漂移补偿结束后,所述数据采集单元335和比较单元337就可以停止工作了,而所述校正单元341则可以一直根据ACW生成单元339提供的ACW对所述频率控制字进行校正或补偿。老化校正或补偿后的频率控制字进入所述相位累加器320,所述相位累加器320以参考频率fR为基础生成表示输入的老化校正后的频率控制字设定频率值的参考频率数据流Posc。需要注意的是,当前权重数值和标准权重数值之间的比较结果能够反映频率漂移的趋势,因此所述ACW生成单元339只需要调整所述ACW以使补偿后的FCW向相反趋势调整就可以了。如果是第一次进行ACW调整,那么所述当前ACW值就是初始ACW,比如为0。

在一个实施例中,所述数据采集单元335采集数字环路滤波器323输出的预定时长(比如3秒,时间越长效果越好)或预定位数(1M位,位数越长效果越好)的数字数据,并对所述数字数据进行权重处理得到一权重数值。在具体实现时,所述数据采集单元335可以采集一段时间的数字数据,并得到一权重数值,之后数据采集单元335可以再接着采集一段时间的数字数据,并得到另一权重数值,之后判断相邻的两个权重值得差值是否在允许范围内,如果是,则说明权重数值已经稳定,随后将稳定后的权重数值提供给所述比较单元337,否则,则说明权重数值仍然不稳定,随后继续得到下一个权重数值,并继续判断该权重数值是否稳定。在一个权重处理示例中,可以将所述数字数据进行累加,其和可以作为权重数值,比如一个10位的二进制序列1100111101的权重数值就是7。在另一个权重处理示例中,可以将所述数字数据进行累加,之后将进行平均,比如还是10位的二进制序列1100111101的权重数值就是7/10=0.7。在其它权重处理示例中,还可以采用一些复杂的平滑处理算法。

在一个实施例中,所述比较单元337输出的所述比较结果包括当前权重数值大于标准权重数值、当前权重数值小于标准权重数值、当前权重数值锁定于标准权重数值。在当前权重数值大于标准权重数值时,所述ACW生成单元339需要调小所述老化校正字ACW,在当前权重数值小于标准权重数值时,所述ACW生成单元339需要调大所述老化校正字ACW,在所述当前权重数值锁定于标准权重数值,所述ACW生成单元339保持所述老化校正字ACW不变。

在一个实施例中,对ACW的每次调整的幅度(即步长)可以根据需要确定,所述步长直接决定了老化频率补偿的速度。通常来说,晶体振荡器的频率漂移一般都很小,比如几赫兹,因此,所述步长也可以比较小。在另一个实施例中,所述ACW生成单元339可以根据当前权重数值和初始权重数值之间的差值来选定调整步长,并根据所述步长对所述ACW进行调整,这样可以加快ACW的调整速度。

在一个实施例中,所述校正单元341根据下式对FCW进行老化校正或补偿:FCWACW=FCW+ACW,校正后的FCWACW进入相位累加器420进行处理。

本发明的一个优点、特点或好处在于:在晶体振荡器出现了老化频率漂移时,通过老化补偿反馈回路的漂移补偿,使得输出频率不受任何影响,而仍能准确地锁定于指定频率上。此外,由于老化补偿反馈回路都是数字电路,易于实现,并且便于集成,并且频率漂移的补偿精度也非常高,理论上可以与FCW的频率控制精度相同,可以轻易达到1Hz或以上的控制精度。从理论上讲,采用模拟电路也可实现老化频率漂移的补偿,比如采用10Mhz/V的压控振荡器(电压每变动1伏特,频率变动10MHz),那么想到达到1Hz的精度,则必须能检测到1/10M=10-7伏特的电压变化,而这在模拟电路领域是很难实现的。

图4示出了本发明中的锁频环400的另一个实施例的结构方框图,所述锁频环400可以用作图2中的锁频环203。图4示出的锁频环400包括有相位累加器420、数字频率比较器421、数字环路滤波器423、D/A转换器425、低通滤波器427、压控振荡器429、分频器433、频率数字转换器431、数据采集单元435、比较单元437、ACW生成单元439以及校正单元441。可以看出,图4中的锁频环400与图3中的锁频环300结构大部分相同,两者不同之处在于:在图4中的锁频环400中用直接频率数字转换器431取代了频率数字转换器331,并且压控振荡器429输出的频率信号fVCO直接提供给所述直接频率数字转换器431,分频器433对压控振荡器429输出的频率信号fVCO进行分频得到输出频率fOUT。

所述直接频率数字转换器431用于直接将压控振荡器429的输出信号转换为数字频率数据流Pvco。对于所述直接频率数字转换器431来说,所述频率采样是通过高频输出信号(比如VCO输出fVCO)采样已知低频参考频率fR实现。本架构的优点之一在于由于用高频的VCO输出Pvco来对低频参考频率fR进行采样,从而提高了频率数字转换器431的精度。通常频率数字转换器的精度是与使用采样频率成比例的。采样频率越高,结果越精确,噪声越低。此外,这种架构简化了反馈路径中的分频器的设计并降低了硬件成本和相关功耗。对于不同的输出频率,分频器433可以被用于分频压控振荡器的输出fVCO以得到需要输出频率。

在图4中的数据采集单元435、比较单元437、ACW生成单元439以及校正单元441同样可以组成老化补偿反馈回路,也可以如同图3一样,对由晶体振荡器的老化而引起的频率漂移进行很好的补偿或校正。

图5示出了本发明中的锁频环500的再一个实施例的结构方框图,所述锁频环500可以用作图2中的锁频环203。图5示出的锁频环500包括有相位累加器501、数字频率比较器503、数字环路滤波器505、增益控制单元507、数控振荡器(digitally controlled oscillator,简称DCO)509、分频器511、频率数字转换器513、数据采集单元535、比较单元537、ACW生成单元539以及校正单元541。可以看出,图5中的锁频环500与图3中的锁频环300结构大部分相同,两者不同之处在于:图5中的锁频环500用增益控制单元507、数控振荡器509分别取代了图3中的锁频环300中的低通滤波器327、压控振荡器329。

所述数控振荡器是通过使用数控电容阵列来替代传统压控振荡器中的压控可变电容器而设计完成。加权开关二进制电容(比如可变电容器)阵列可以通过二进级数字控制信号切换至高电容模式或低电容模式。通过使用delta-sigma调制的数控位就可以获得高分辨率的电容值。如图5所示,相位累加器501、数字频率比较器503、数字环路滤波器505、反馈路径中的分频器511及频率数字转换器513与图3中的相应模块具有相同的功能。

所述数字环路滤波器505的输出连接至增益控制单元507的输入,所述增益控制单元507可以生成用于控制数控振荡器的加权开关二进制电容阵列的数字控制信号。所述增益控制单元507用于归一化数控振荡器增益并消除来自工艺、电压和温度的对数控振荡器相位和频率的影响。所述数控振荡器609根据来自增益控制单元507的数字信号生成的频率信号fDCO。当环路锁定后,通过使用数字频率比较器503,数字频率数据流Pvco被锁定至参考频率数据流Posc。这样,数控振荡器509的输出被锁定于频率控制字FCW设定的期望频率。

如图5所示,通过利用数控振荡器来替代压控振荡器从而可以去除图3中的数字模拟转换器和低通滤波器,这样整个锁频环500可以通过全数字逻辑方式实现。这样,频率信号将不容易受到噪声和其他环境的影响。这种架构尤其适合低压、深亚微米COMS工艺,因为传统模拟振荡器的的线性范围由于低电压而变得很小,并且具有较高增益,这使模拟压控振荡器极易受到噪声和工作点漂移的影响,但是,采用数字压控振荡器就将不容易受到低电压和其他环境的因素的影响。

同样的,在图5中的数据采集单元535、比较单元537、ACW生成单元539以及校正单元541同样可以组成老化补偿反馈回路,也可以如同图3一样,对由晶体振荡器的老化而引起的频率漂移进行很好的补偿或校正。

图6示出了本发明中的锁频环600的另外一个实施例的结构方框图,所述锁频环600可以用作图2中的锁频环203。图6示出的锁频环600包括有相位累加器601、数字频率比较器603、数字环路滤波器605、增益控制单元607、数控振荡器609、分频器611、直接频率数字转换器613、数据采集单元635、比较单元637、ACW生成单元639以及校正单元641。可以看出,图6中的锁频环600与图5中的锁频环500结构大部分相同,两者不同之处在于:在图6中的锁频环600中用直接频率数字转换器613取代了图5中的频率数字转换器513,并且数控振荡器509输出的频率信号fDCO直接提供给所述直接频率数字转换器613,分频器611对数控振荡器609输出的频率信号fDCO进行分频得到输出频率fOUT。

同样的,在图6中的数据采集单元635、比较单元637、ACW生成单元639以及校正单元641同样可以组成老化补偿反馈回路,也可以如同图3一样,对由晶体振荡器的老化而引起的频率漂移进行很好的补偿或校正。

在一个实施例中,也可以不使用分频器对所述数控振荡器或压控振荡器的输出信号进行分频,而直接用所述数控振荡器或压控振荡器的输出信号作为期望输出频率。在不同实施例中的所述频率数字转换器和所述直接频率数字转换器在实现原理上是完全一样的,他们都可以被叫做频率数字转换器。

以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换等,均应包含在本发明的保护范围之内。

频率合成器及锁频环专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0