专利摘要

本发明提供的眼开监视器装置在实现信号眼图测试时,使用两个与信号频率相同的眼开测量时钟对所设置的相位点上的眼图打开大小进行测试;设置阈值大小以及在半个周期内对测量时钟相位进行设置;判断所设置的阈值大小在测量时钟处是否在眼图内部,满足在眼图内部的最大阈值便是该时钟相位点处的眼图打开大小;将每个相位点上的眼图打开大小结果保存到寄存器中,在测试完所有相位点后将寄存器的值依序排列,得到了信号眼图的水平与垂直打开大小值。与现有技术相比,本发明提出的眼开监视器电路装置具有无需进行初始时钟与数据的同步操作,测试过程设置与测试结果记录由数字控制模块自动完成,可获得一个周期内信号眼图打开大小信息的特点。

权利要求

1.一种应用于高速串行器/解串器的信号眼图测试方法,其特征在于,包括如下步骤:

S10,使用两个与信号频率相同的眼开测量时钟对所设置的相位点上的眼图打开大小进行测试,所述两个测量时钟分别覆盖半个周期;

S20,设置阈值大小以及在半个周期内对测量时钟相位进行设置;

S30,判断所设置的阈值大小在测量时钟处是否在眼图内部,满足在眼图内部的最大阈值便是该时钟相位点处的眼图打开大小;

S40,将每个相位点上的眼图打开大小结果保存到寄存器中,在测试完所有相位点后将寄存器的值依序排列,得到了信号眼图的水平与垂直打开大小值。

2.一种应用于高速串行器/解串器的眼开监视器装置,其特征在于,包括:阈值线测试电路、时钟与阈值设置电路、设置寄存器、有限状态机、结果监测电路和测试结果寄存器,其中:

阈值线测试电路,接收外部被测输入信号和时钟与阈值设置电路输出的两个阈值信号和两个眼开测量时钟信号来对所设置的相位点上的眼图打开大小进行测试,并输出相应的测试结果;所述两个眼开测量时钟信号与输入信号频率相同且两个测量时钟分别覆盖半个周期;

结果监测电路,接收阈值线测试电路输出的每个相位点上的眼图打开大小结果并输出;

时钟与阈值设置电路,用于在半个周期内对测量时钟相位进行设置以及对阈值的大小设置;

有限状态机,对时钟与阈值设置电路中阈值和测试时钟的相位设置进行控制,并对结果监测电路的输出进行处理,将测试结果保存到测试结果寄存器中;

设置寄存器,用于将有限状态机的控制信号转化为时钟与阈值设置电路中的时钟与阈值设置的控制信号;

测试结果寄存器,用于保存每个相位点上的眼图打开大小结果,并在测试完所有相位点后将结果值依序排列,得到了信号眼图的水平与垂直打开大小值。

3.根据权利要求2所述的眼开监视器装置,其特征在于,所述时钟与阈值设置电路包括数模转换电路和相位旋转器,所述设置寄存器包括相位设置寄存器和电压设置寄存器;

所述相位旋转器用于在半个周期内对测量时钟相位进行设置并输出;

所述数模转换电路用于对阈值的大小进行设置并输出;

所述相位设置设置寄存器连接相位旋转器,用于将有限状态机的控制信号转化为测量时钟相位的控制信号;

所述电压设置寄存器连接数模转换电路,用于将有限状态机的控制信号转化为阈值大小设置的控制信号。

4.根据权利要求3所述的眼开监视器装置,其特征在于,所述阈值线测试电路中,第一比较器(233)的高电平输入端连接外部输入数据,其低电平输入端连接一阈值信号,其输出端同时连接第一、第二D触发器(201、202)的输入端,所述第一D触发器(201)的输出端连接第一异或门(208)的一输入端,所述第一异或门(208)的输出端连接第一SR所存器(217)的一输入端,所第二述D触发器(202)的输出端连接第二异或门(205)的一输入端,所述第二异或门(205)的输出端连接第二SR所存器(218)的一输入端;第二比较器(234)的高电平输入端连接外部输入数据,其低电平输入端连接另一阈值信号,其输出端同时连接第三、第四D触发器(203、204)的输入端,所述第三D触发器(203)的输出端连接第一异或门(208)的另一输入端,所述第四D触发器(204)的输出端连接第二异或门(205)的另一输入端,所述第一、第二SR所存器(217、218)的输出端分别连接有限状态机的输入端。

5.根据权利要求4所述的眼开监视器装置,其特征在于,所述第一、二比较器(233、234)由一个吉尔伯特单元和两级预放大器构成。

说明书

技术领域

本发明涉及高速串行器/解串器系统中高速信号的眼图测试电路设计领域,具体为一种用于高速串行器/解串器的眼开监视器装置及测试方法。

背景技术

串行数据在链路中传输时,由于系统传输总特性(包括均衡器和信道的特性)不理想,导致前后码元的波形畸变、展宽,并使前面波形出现很长的拖尾,影响到当前码元的抽样时刻,从而对当前码元的判决造成干扰,这就是所谓的码间干扰现象。随着数据速率的提升,码间干扰现象也更加显著。一般采用数据眼图对码间干扰量进行衡量。在高速的串行链路传输系统中,发送端采用片上的伪随机比特发生器产生测试序列。在接收端,对于接收信号眼图的获取由片上的眼开监视器获得。片上眼开监视器可以提供眼图的打开大小信息,甚至是完整的眼图形状。

目前片上眼开监视器可以划分为一维眼开监视器,二维眼开监视器,基于边缘数据的眼开监视器,以及多采样眼开监视器。

一维眼开监视器对眼图的垂直张开程度进行测量,一维眼开监视器的硬件开销最小,然而一维眼开监视器只能监测眼图的垂直方向,无法获知眼图的水平打开大小。

二维眼开监视器同时在垂直和水平方向上对眼图进行监测。二维眼开监视器基本思想是通过形状为矩形的模板与数据进行比较,如果测试数据穿过了模板则认为对应的模板是不可用的,将所有未穿过数据的模板进行叠加,便获得了最终的数据眼图。但是该电路测试时,模板的起始时钟位置需要与数据中心对齐,其对齐操作是通过让测试数据经过延迟线实现的。

基于边缘数据的眼开监视器对眼图张开的监测是通过检查数据边沿实现的,边沿的监测通常需要密集采样,所得到的结果使用直方图进行表示,直方图越窄,眼图打开得越大,但是当数据速率过高时,受采样时钟频率的限制,使用基于边缘数据的眼开监视器测量眼图将变得困难。

多采样眼开监视器在每一个周期内,通过大量采样对数据的一个周期内多个相位点上的垂直打开大小进行采样,需要设计十分精确的相位旋转器,多采样眼开监视器的监测是最全面的,但是其硬件设计复杂度最大。

由于一维眼开监视器只能对眼图的垂直打开大小进行测量,而基于边缘数据的眼开监视器对于高速率数据受限于采样频率的提高,多采样眼开监视器需要十分精确的相位旋转器与多相位点采样,而二维眼开监视器对眼图的测试取决于模板的选择,其只能对设定的模板进行测试,其测试结果只能说明给定的模板是否可用,最终的眼图需要进行大量的模板设置与测试工作,费时费力。

发明内容

本发明要解决的技术问题是二维眼开监视器如何不通过时钟与数据的同步而获取信号眼图,继而从眼图中可以得到最佳采样时刻,判决门限电平等信息,这些信息主要是通过眼图的水平打开程度和垂直打开程度体现出来的。随着信号受噪声量的加大,水平与垂直的打开程度会随之减少。本发明在于如何测量出眼图的水平与垂直打开大小,即眼图的打开程度。本发明通过结合时钟周期遍历和阈值线比较两种方法,简化了测试方法及监视装置,其具体方案如下:

一种应用于高速串行器/解串器的信号眼图测试方法,包括如下步骤:

S10,使用两个与信号频率相同的眼开测量时钟对所设置的相位点上的眼图打开大小进行测试,所述两个测量时钟分别覆盖半个周期;

S20,设置阈值大小以及在半个周期内对测量时钟相位进行设置;

S30,判断所设置的阈值大小在测量时钟处是否在眼图内部,满足在眼图内部的最大阈值便是该时钟相位点处的眼图打开大小;

S40,将每个相位点上的眼图打开大小结果保存到寄存器中,在测试完所有相位点后将寄存器的值依序排列,得到了信号眼图的水平与垂直打开大小值。

本发明的另一目的还在于提供一种应用于高速串行器/解串器的眼开监视器装置,包括:阈值线测试电路、时钟与阈值设置电路、设置寄存器、有限状态机、结果监测电路和测试结果寄存器,其中:

阈值线测试电路,接收外部被测输入信号和时钟与阈值设置电路输出的两个阈值信号和两个眼开测量时钟信号来对所设置的相位点上的眼图打开大小进行测试,并输出相应的测试结果;所述两个眼开测量时钟信号与输入信号频率相同且两个测量时钟分别覆盖半个周期;

结果监测电路,接收阈值线测试电路输出的每个相位点上的眼图打开大小结果并输出;

时钟与阈值设置电路,用于在半个周期内对测量时钟相位进行设置以及对阈值的大小设置;

有限状态机,对时钟与阈值设置电路中阈值和测试时钟的相位设置进行控制,并对结果监测电路的输出进行处理,将测试结果保存到测试结果寄存器中;

设置寄存器,用于将有限状态机的控制信号转化为时钟与阈值设置电路中的时钟与阈值设置的控制信号;

测试结果寄存器,用于保存每个相位点上的眼图打开大小结果,并在测试完所有相位点后将结果值依序排列,得到了信号眼图的水平与垂直打开大小值。

进一步的,所述时钟与阈值设置电路包括数模转换电路和相位旋转器,所述设置寄存器包括相位设置寄存器和电压设置寄存器;

所述相位旋转器用于在半个周期内对测量时钟相位进行设置并输出;

所述数模转换电路用于对阈值的大小进行设置并输出;

所述相位设置设置寄存器连接相位旋转器,用于将有限状态机的控制信号转化为测量时钟相位的控制信号;

所述电压设置寄存器连接数模转换电路,用于将有限状态机的控制信号转化为阈值大小设置的控制信号。

进一步的,所述阈值线测试电路中,第一比较器的高电平输入端连接外部输入数据,其低电平输入端连接一阈值信号,其输出端同时连接第一、第二D触发器的输入端,所述第一D触发器的输出端连接第一异或门的一输入端,所述第一异或门的输出端连接第一SR所存器的一输入端,所第二述D触发器的输出端连接第二异或门的一输入端,所述第二异或门的输出端连接第二SR所存器的一输入端;第二比较器的高电平输入端连接外部输入数据,其低电平输入端连接另一阈值信号,其输出端同时连接第三、第四D触发器的输入端,所述第三D触发器的输出端连接第一异或门的另一输入端,所述第四D触发器的输出端连接第二异或门的另一输入端,所述第一、第二SR所存器的输出端分别连接有限状态机的输入端。

进一步的,所述第一、二比较器由一个吉尔伯特单元和两级预放大器构成。

与现有技术相比,本发明通过对眼图一个周期内各相位点处眼图打开程度的测试,将各测试结果叠加得到信号眼图。与传统的二维眼开监视器相比,本发明提出的眼开监视器电路装置具有无需进行初始时钟与数据的同步操作,测试过程设置与测试结果记录由数字控制模块自动完成,可获得一个周期内信号眼图打开大小信息的特点。

附图说明

下面结合附图对本发明的具体实施方式作进一步详细说明。

图1为本发明实施例的眼开监视器的结构图。

图2为本发明实施例的眼开监视器的电路结构图。

图3为本发明实施例的相位旋转器的电路结构图。

图4为本发明实施例的数模转换电路图。

图5为本发明实施例的比较器电路图。

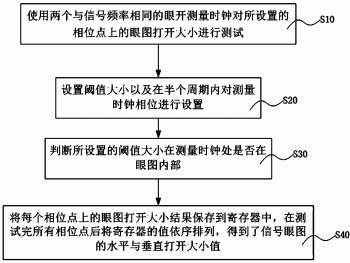

图6为本发明实施例的信号眼图测试方法的流程图。

具体实施方式

为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

附图6为本发明实施例的信号眼图测试方法的流程图:包括如下步骤:

S10,使用两个与信号频率相同的眼开测量时钟对所设置的相位点上的眼图打开大小进行测试,所述两个测量时钟分别覆盖半个周期;

S20,设置阈值大小以及在半个周期内对测量时钟相位进行设置;

S30,判断所设置的阈值大小在测量时钟处是否在眼图内部,满足在眼图内部的最大阈值便是该时钟相位点处的眼图打开大小;

S40,将每个相位点上的眼图打开大小结果保存到寄存器中,在测试完所有相位点后将寄存器的值依序排列,得到了信号眼图的水平与垂直打开大小值。

在实现信号眼图测试时,使用两个与信号频率相同的眼开测量时钟对所设置的相位点上的眼图打开大小进行测试,两个时钟分别覆盖半个周期,通过四象限相位旋转器在半个周期内对测量时钟相位进行设置;测试电路判断出所设置的阈值大小在测量时钟处是否在眼图内部,满足在眼图内部的最大阈值便是该时钟相位点处的眼图打开大小;将每个相位点上的眼图打开大小结果通过控制电路保存到寄存器中,在测试完所有相位点后将寄存器的值依序排列,便得到了信号眼图的水平与垂直打开大小值。本发明通过有限状态机完成阈值线设置,测试结果保存在寄存器中,通过读取寄存器中的值便能获取测试信号的眼图。

附图1是眼开监视器一实施例的结构示意图。如图1所示,本眼开监视器电路由阈值线测试电路110和控制模块120两大部分组成。阈值线测试电路110对控制模块120的输出阈值信号VH和VL在给定的测试时钟信号CLK_RIGHT和CLK_LEFT处对输入信号VIN 进行测试,并输出相应的测试结果信号errorL和errorR。

控制模块120的核心是有限状态机124。有限状态机124对阈值和测试时钟的相位设置进行控制,并对结果监测电路的输出进行处理,将测试结果保存到测试结果寄存器122中。

设置寄存器123将有限状态机124的控制信号转化为模拟电路121中的时钟与阈值设置电路的控制信号。为了完成对测试时钟的设置,除了需要控制信号外,还需要外部时钟的输入作为参考时钟,如图1所示,信号I是与输入信号同频的时钟信号,但两者的相位并没有确定的关系,信号Q是与信号I 同频且90度正交的时钟信号,信号I’与信号Q’ 分别是信号I和信号Q的反相信号。当控制模块120完成了所有的阈值设置和测试后,测试结果寄存器122中便保存了一个周期内信号眼图的打开信息,此时信号FINISH 置高电平,表示测试完成。如果需要再次对输入信号的眼图进行测试,使信号RESET 置低电平即可。

如图2所示,对图2中的全定制模块给出了具体的电路结构。图1模拟电路 121中的时钟与阈值设置电路分别由两个相位旋转器 231和数模转换电路 232实现。相位旋转器 231的四个参考时钟信号I、I’、Q、Q’两两正交,且与输入信号VIN 同频。相位设置寄存器222根据有限状态机223给定的相位计数器227的值输出象限选择信号225,选择四个参考时钟中的两个作为参考时钟,通过权重控制信号226使输出时钟的相位位于选定的两个参考时钟之间。当相位计数器227的值为“0”时,信号CLK_LEFT 和信号CLK_RIGHT 与信号I具有相同的相位;当计数器的值最大时,信号CLK_LEFT和CLK_RIGHT 与I’ 具有相同的相位。计数器的值每加“1”时,CLK_LEFT 和CLK_RIGHT的相位分别向左右移动相应的大小。

CLK_LEFT 和CLK_RIGHT的相位各占用半个周期,即180度,通过相位旋转器由数据中心向两边移动的过程中,相位旋转器 231将进行一次参考时钟的重新选择,时钟与象限的对应关系如表 1所示,相位旋转器 231象限由象限选择信号 225进行控制。

表 1 时钟与象限对应关系

由于相位旋转器 231将对与信号同频的全速时钟进行一个周期的移相操作,因此,采样时钟起始位置信号I与眼图中心并不需要对齐,通过对时钟进行一个周期的移相遍历,可得到一个周期内的眼图的全部信息。

输入数据VIN 与两个阈值电压的比较分别由两个比较器233和234完成。数据连续地与阈值信号VH 和VL 进行比较,比较结果在采样时钟阈值信号CLK_LEFT 和CLK_RIGHT 处获得。比较器233对VIN 和VH 进行比较,当VIN 大于VH 时,比较器输出为高电平,小于时,输出低电平;比较器234对VIN 和VL 进行比较,当VIN 大于VL时,比较器输出为高电平,小于VL,输出低电平。

D触发器201和D触发器202分别在CLK_LEFT 和CLK_RIGHT 时间点处采样VIN和VH 的比较结果;D触发器203和D触发器204分别在CLK_LEFT 和CLK_RIGHT 时间点处采样输入数据和VL的比较结果。将D触发器201的输出信号SH_LEFT 和D触发器203的输出信号SL_LEFT进行异或,为加大驱动能力,将异或结果经过了两级反相器209和210后便得到了在时间点CLK_LEFT处的错误信号errorL,类似的,可得到在时间点CLK_RIGHT处的错误信号errorR 。errorL或errorR为高电平,说明信号穿过了由VH和VL构成的阈值线,反之信号在阈值线外。

对于高速信号,经过电路得到的errorL或errorR信号的最小脉宽为皮秒量级,设计两个全定制的SR锁存器217、218,一旦接收到errorL或errorR为高电平时,对应的SR锁存器将输出高电平,直到有限状态机223在进行阈值线设置时将输出清零。

有限状态机223依次对一个周期内的各相位点处的眼开大小进行测量,并将测量结果 信号按序保存到测试结果寄存器中,将所有的测量结果在一个周期内进行排列,便可以得到信号眼图的水平与垂直打开大小的信息。

附图3为相位旋转器 231电路结构图,内插权重与象限控制信号来自于相位设置寄存器 222。通过适当地调节差分控制线,拖尾电流被控制,以此来设置输入的相位权重并获得所需的内插相位。为了产生均匀的相位步长,从而均匀地扫描眼图水平张开程度,相位旋转器的传输特性,即,输出相位和输入权重之间的关系,应是线性的。

在输出时钟上升沿位置从初始时钟向左右两边移动过程中,相位旋转器231需进行一次象限调整,象限调整由图3中的标号为N2_1—N2_4的NMOS控制,控制线名称为POL,其中POL_I1与POL_I0控制I的象限;POL_Q1与POL_Q0控制Q的象限。当POL_I1=1,POL_I0=0时,I路信号为正;当POL_I1=0,POL_I0=1时,I路信号为负;Q路信号与I路信号类似。象限与象限控制位的对应关系如表 2所示,表中控制位顺序为POL_I1 - POL_I0 - POL_Q1 - POL_Q0:

表 2 象限与控制位关系

当输入权重为0时,输出时钟的上升沿位于初始时钟处,随着输入权重的逐步加大,输出时钟上升沿分别向设定的方向移动。步长的大小是由是由输入的控制权重个数决定的,如果步长设置过大,则测量精度不高,步长设置过小,则可能由于D触发器建立时间的限制,需要多次调整才能采到所需要的数据,从而影响测量效率。步长的大小,也就是输入的控制权重的个数应根据实际电路的参数进行确定。

附图4为数模转换电路232的电路原理图,其是将电压设置寄存器224给出的控制信号转换为模拟信号,在本发明中,初始状态数模转换电路的输出VH和VL均为共模值,控制信号每加“1”,VH增大一个步长,VL减小一个步长。电压设置寄存器224的功能类似于一个编码器,其输入为控制阈值的计数器值,输出为若干对差分控制信号。当计数器值为全零时,差分控制信号的一半为“1”,一半为“0”,数模转换电路的输出VH和VL为共模值。随着计数器的值每增大1,差分控制信号中“1”的个数会增多一个,“0”的个数会减少一个。

数模转换电路的工作原理是通过控制信号控制电流分配实现的。如图4所示电路中,奇数号MOS管控制着VL的大小,偶数号MOS管控制着VH的大小。当控制信号中一半为“1”,一半为“0”时,流过两个电阻的电流相同,此时VH和VL值相同,通过R值与尾电流的设计,使该值为共模值;随着“1”“0”个数的变化,电流值将在两个电阻间重新分配,且其总值保持不变。

附图5为本实施例的比较器的电路图,比较器233、234电路如图5所示,由一个吉尔伯特单元和两级预放大器构成。吉尔伯特单元的输出为输入的差分信号与差分参考电平之间的差值,由于这个信号幅值过小,并不能直接用于后级D触发器的输入,因此需要两级预放大器进行放大,以保证后级D触发器可以采到正确的信号幅值。每一级放大器采用了相同有源反馈结构,这种放大器的带宽大于传统的差分放大器带宽。

本发明提出了用于测量高速信号眼图的眼开监视器电路装置,通过对眼图一个周期内各相位点处眼图打开程度的测试,将各测试结果叠加得到信号眼图。与传统的二维眼开监视器相比,本发明提出的眼开监视器电路装置具有无需进行初始时钟与数据的同步操作,测试过程设置与测试结果记录由数字控制模块自动完成,可获得一个周期内信号眼图打开大小信息的特点。

最后,还需要注意的是,以上列举的仅是本发明的一个具体实施例。显然,本发明不限于以上实施例,还可以有许多变形。本领域的普通技术人员能从本发明公开的内容直接导出或联想到的所有变形,均应认为是本发明的保护范围。

用于高速串行器/解串器的眼开监视器装置及测试方法专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0