专利摘要

本发明针对现有时钟生成方法设计复杂、占用资源多、存在时钟漂移和时延误差的问题,公开了一种基于GPS秒脉冲的2的幂次方倍频方法,属于数字信号处理领域。本发明通过所述二进制除法规则设计、以GPS秒脉冲测量本地晶振时钟漂移、将倍频累加寄存器的溢出位作为输出时钟等步骤,实现了GPS秒脉冲的2的幂次方倍频,本发明设计简单、易于实现、占用资源少,消除了本地晶振时钟漂移与除法器时延误差,使生成时钟信号的1秒以上长期精度与GPS秒脉冲精度一致,使生成时钟信号的1秒以内短期精度与消除时钟漂移后的本地时钟一致,提高了生成时钟信号的精度。本发明可用于为FPGA中各数字信号处理模块提供所需的时钟信号,可使系统简化设计、提高处理精度。

权利要求

1.一种基于GPS秒脉冲的2的幂次方倍频方法,其特征在于包括以下步骤:

步骤S1:CLK为倍频方法输出时钟,F_LOCAL为本地高频晶振时钟的频率;CLK频率的理论值是2的幂次方,通过对数运算确定其频率的理论值为2的M次幂;F_LOCAL除以CLK频率的商是实现倍频所需参数,将F_LOCAL以二进制表示,以F_LOCAL二进制表示形式的第1位至第M+1位作为商的小数部分B;以F_LOCAL二进制表示形式的第M+2位至最高位作为商的整数部分A;

步骤S2:设立本地晶振时钟频率计数寄存器CLK_LOCAL_1、CLK_LOCAL_2,CLK_LOCAL_1、CLK_LOCAL_2初始化为零;

步骤S3:在GPS秒脉冲第一次到来时,使用寄存器CLK_LOCAL_1开始对本地高频晶振时钟频率F_LOCAL进行累加计数,每次累加值为1,当以后每一次GPS秒脉冲到来时,用寄存器CLK_LOCAL_1的值减去寄存器CLK_LOCAL_2的值以获得本地高频晶振时钟频率F_LOCAL的测量值,而后将寄存器CLK_LOCAL_1的值存储到寄存器CLK_LOCAL_2中;

步骤S4:由F_LOCAL的测量值计算步骤S1中所述商的整数部分A和步骤S1中所述商的小数部分B;

步骤S5:设立倍频累加寄存器QUOTIENT,倍频累加寄存器QUOTIENT最大容量值的二进制表示位数与整数部分A的二进制表示位数相同;

步骤S6:设立小数累加寄存器REMAINDER,小数累加寄存器REMAINDER最大容量值的二进制表示位数与小数部分B的二进制表示位数相同;

步骤S7:将倍频累加寄存器QUOTIENT的初始值设置为其最大值减去整数部分A;

步骤S8:以本地晶振时钟上升沿为触发条件,倍频累加寄存器QUOTIENT开始累加,每次累加1;

步骤S9:以倍频累加寄存器QUOTIENT溢出为触发条件,小数累加寄存器REMAINDER开始累加,每次累加B;

步骤S10:当倍频累加寄存器QUOTIENT溢出时,将倍频累加寄存器QUOTIENT的值重置为其最大值减去整数部分A;

步骤S11:当小数累加寄存器REMAINDER溢出时,倍频累加寄存器QUOTIENT减1;

步骤S12:将倍频累加寄存器QUOTIENT的溢出位作为输出的时钟信号CLK。

说明书

技术领域

本发明涉及倍频技术,具体涉及一种基于GPS(Global Position System,全球定位系统)秒脉冲的2的幂次方倍频方法,应用于基于FPGA(Field Programmable Gate Array,现场可编程门阵列)的数字信号处理系统设计中,为FPGA中各数字信号处理模块提供所需的时钟信号。

背景技术

时钟信号是数字信号处理模块工作所必须的输入信号,通常是将晶体振荡器输出时钟进行处理以获得所需频率的时钟信号。近年来,工业界研发了各种时钟信号产生技术,主要是基于除法器实现,具体来说是利用除法器计算输入时钟频率与输出时钟频率的倍数关系,而后以此倍数关系确定参数,进而以此参数对输入时钟进行处理而获得所需频率的时钟信号。这种技术有三个主要的缺点,首先是本地晶振时钟频率不可避免的漂移将引起输出时钟频率的漂移;其次是使用除法器计算参数,将占用FPGA的大量片内资源且设计复杂;最后是除法器计算的延时将带来输出时钟频率的误差。GPS秒脉冲是精度很高的时钟信号,其精度能够满足大多数数字信号处理模块对时钟信号的精度需求,但其频率为固定的1Hz,无法被FPGA中各数字信号处理模块直接使用。因此,寻找一种设计简单、占用资源少、不存在时钟漂移和时延误差的基于GPS秒脉冲的时钟信号倍频产生方法具有十分重要的意义。

发明内容

本发明的目的是为解决目前基于除法器的时钟信号产生方法无法消除输入时钟漂移、设计复杂、占用FPGA大量资源、存在时延误差等问题,提供了一种基于GPS秒脉冲的2的幂次方倍频方法。该方法能够以高精度GPS秒脉冲为输入信号,产生GPS秒脉冲的2的幂次方倍频时钟信号,通过使用GPS秒脉冲测量本地高频晶振时钟信号的实际频率以消除晶振频率的漂移,利用左移即为二进制除法来实现倍频参数的计算,避免了使用除法器,使时钟信号产生方法简单、占用FPGA资源少且没有时延误差。

为实现上述发明目的,本发明采用如下技术方案:

一种基于GPS秒脉冲的2的幂次方倍频方法,该方法包括以下步骤:

步骤S1:CLK为倍频方法输出时钟,F_LOCAL为本地高频晶振时钟的频率;CLK频率的理论值是2的幂次方,通过对数运算确定其频率的理论值为2的M次幂;F_LOCAL除以CLK频率的商是实现倍频所需参数,将F_LOCAL以二进制表示,以F_LOCAL二进制表示形式的第1位至第M+1位作为商的小数部分B;以F_LOCAL二进制表示形式的第M+2位至最高位作为商的整数部分A;

步骤S2:设立本地晶振时钟频率计数寄存器CLK_LOCAL_1、CLK_LOCAL_2,CLK_LOCAL_1、CLK_LOCAL_2初始化为零;

步骤S3:在GPS秒脉冲第一次到来时,使用寄存器CLK_LOCAL_1开始对本地高频晶振时钟频率F_LOCAL进行累加计数,每次累加值为1,当以后每一次GPS秒脉冲到来时,用寄存器CLK_LOCAL_1的值减去寄存器CLK_LOCAL_2的值以获得本地高频晶振时钟频率F_LOCAL的测量值,而后将寄存器CLK_LOCAL_1的值存储到寄存器CLK_LOCAL_2中;

步骤S4:由F_LOCAL测量值计算步骤S1中所述商的整数部分A和步骤S1中所述商的小数部分B;

步骤S5:设立倍频累加寄存器QUOTIENT,倍频累加寄存器QUOTIENT最大容量值的二进制表示位数与整数部分A的二进制表示位数相同;

步骤S6:设立小数累加寄存器REMAINDER,小数累加寄存器REMAINDER最大容量值的二进制表示位数与小数部分B的二进制表示位数相同;

步骤S7:将倍频累加寄存器QUOTIENT的初始值设置为其最大值减去整数部分A;

步骤S8:以本地晶振时钟上升沿为触发条件,倍频累加寄存器QUOTIENT开始累加,每次累加1;

步骤S9:以倍频累加寄存器QUOTIENT溢出为触发条件,小数累加寄存器REMAINDER开始累加,每次累加B;

步骤S10:当倍频累加寄存器QUOTIENT溢出时,将倍频累加寄存器QUOTIENT的值重置为其最大值减去整数部分A;

步骤S11:当小数累加寄存器REMAINDER溢出时,倍频累加寄存器QUOTIENT减1;

步骤S12:将倍频累加寄存器QUOTIENT的溢出位作为输出的时钟信号CLK。

通过以上步骤,实现了基于GPS秒脉冲的2的幂次方倍频。

与现有的技术相比,本发明具有以下优点:

通过GPS秒脉冲消除了本地晶振时钟频率的漂移,利用二进制表示获得除法运算结果,避免使用专用除法器模块,简化了系统设计、降低了FPGA资源消耗,避免了除法器模块时延带来的误差;

附图说明:

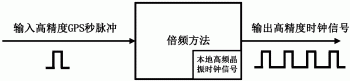

1.图1为本发明实施例的结构图;

2.图2为本发明实施例的工作流程图;

3.图3为本发明具体实施方式步骤S3的仿真结果;

4.图4为本发明具体实施方式步骤S4的仿真结果;

5.图5为本发明具体实施方式步骤S12的仿真结果。

具体实施方式:

下面将结合说明书附图和具体实施例对本发明作进一步详细说明。

如图1所示,为一种基于GPS秒脉冲的2的幂次方倍频方法实施例的结构图,图2为本实施例的流程图,具体包括以下步骤:

步骤S1:F_LOCAL为本地高频晶振时钟信号频率,频率的理论值为62.5MHz;CLK为倍频方法输出时钟,CLK频率的理论值为4096Hz,4096是2的幂次方,通过对数运算确定其频率的理论值为2的12次幂;F_LOCAL除以CLK频率的商是实现倍频所需参数,将F_LOCAL以二进制表示,以F_LOCAL二进制表示形式的第1位至第(12+1)位作为商的小数部分B;以F_LOCAL二进制表示形式的第(12+2)位至最高位作为商的整数部分A;

步骤S2:设立本地晶振时钟频率计数寄存器CLK_LOCAL_1、CLK_LOCAL_2,CLK_LOCAL_1、CLK_LOCAL_2初始化为零;

步骤S3:如图3所示,在GPS秒脉冲第一次到来时(GPS秒脉冲由图3中one_pps表示),使用寄存器CLK_LOCAL_1开始对本地高频晶振时钟频率F_LOCAL进行累加计数(F_LOCAL由图3中sysclk62p5MHz表示),每次累加值为1,当以后每一次GPS秒脉冲到来时,用寄存器CLK_LOCAL_1的值减去寄存器CLK_LOCAL_2的值以获得本地高频时钟频率F_LOCAL的测量值,而后将寄存器CLK_LOCAL_1的值存储到寄存器CLK_LOCAL_2中;本地高频晶振时钟的理论值为62.5MHz,而实际测量的结果为62.500499MHz,有效消除了本地晶振时钟漂移带来的影响;

步骤S4:如图4所示,由F_LOCAL的测量值计算步骤S1中所述商的整数部分A和步骤S1中所述商的小数部分B;此计算过程在1个本地晶振时钟节拍完成,避免了使用除法器带来的时延误差;

步骤S5:设立倍频累加寄存器QUOTIENT,倍频累加寄存器QUOTIENT最大容量值的二进制表示位数与整数部分A的二进制表示位数相同;

步骤S6:设立小数累加寄存器REMAINDER,小数累加寄存器REMAINDER最大容量值的二进制表示位数与小数部分B的二进制表示位数相同;

步骤S7:将倍频累加寄存器QUOTIENT的初始值设置为其最大值减去整数部分A;

步骤S8:以本地晶振时钟上升沿为触发条件,倍频累加寄存器QUOTIENT开始累加,每次累加1;

步骤S9:以倍频累加寄存器QUOTIENT溢出为触发条件,小数累加寄存器REMAINDER开始累加,每次累加B;

步骤S10:当倍频累加寄存器QUOTIENT溢出时,将倍频累加寄存器QUOTIENT的值重置为其最大值减去整数部分A;

步骤S11:当小数累加寄存器REMAINDER溢出时,倍频累加寄存器QUOTIENT减1;

步骤S12:如图5所示,clk_divider_rising和clk_divider_faling信号为QUOTIENT的溢出标志,倍频累加寄存器QUOTIENT的溢出位即是输出时钟信号CLK。

本实施例是基于Xilinx公司的Spartan-6型FPGA芯片设计,其对FPGA资源的消耗与传统方法对比如表1所示,可以看到本实施例所消耗的PFGA资源与传统方法相比,减小了约10倍。

使用本发明所生成的时钟信号,其1秒以上的长期精度与GPS秒脉冲精度一致;其1秒以内的短期精度与消除漂移后的本地晶振时钟精度一致,而传统方法所生成的时钟信号精度与含有漂移的本地晶振时钟精度一致,因此本发明所生成时钟信号精度高于传统方法。

表1FPGA资源消耗对比

以上仅是本发明的优选实施方式,本发明的保护范围并不仅限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,应当视为落入本发明的保护范围。

一种基于GPS秒脉冲的2的幂次方倍频方法专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0