专利摘要

本发明公开了一种用于智能变电站合并单元的守时误差检测方法,步骤包括:通过标准时钟源向被测合并单元输出光IRIG-B码并计时,获取被测合并单元输出的每一帧0标号报文的第一个比特时间与光IRIG-B码秒沿之间的时间偏移的最小值;拔掉被测合并单元的光IRIG-B码输入并开始计时,获取被测合并单元输出的每一帧0标号报文的第一个比特时间与光IRIG-B码秒沿之间的时间偏移的最大值;将前述的最大值减去最小值得到被测合并单元的守时误差。本发明直接测量报文的守时误差,所测结果更能反映合并单元守时误差对报文接收IED设备的影响,且具有守时误差检测准确性高、检测方便快捷、应用范围广的优点。

权利要求

1.一种用于智能变电站合并单元的守时误差检测方法,其特征在于步骤包括:

1)通过标准时钟源向被测合并单元输出光IRIG-B码并开始计时,获取接收到被测合并单元输出的每一帧0标号报文的第一个比特时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移△T1,在指定的计时时间内找出所述时间偏移的最小值△T1min;

2)保持标准时钟源的光IRIG-B码输出、拔掉被测合并单元的光IRIG-B码输入并开始计时,获取接收到被测合并单元输出的每一帧0标号报文的第一个比特时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移△T2,在指定的计时时间内找出所述时间偏移的最大值△T2max;

3)将所述最大值△T2max减去最小值△T1min,得到指定的计时时间内被测合并单元的守时误差△Tm。

2.根据权利要求1所述的用于智能变电站合并单元的守时误差检测方法,其特征在于,所述步骤1)和步骤2)中获取接收到被测合并单元输出的每一帧0标号报文的第一个比特时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移的详细步骤包括:

1.1)接收被测合并单元输出的每一个报文帧;

1.2)解析并提取出所述接收报文帧中的报文;

1.3)根据本地的时钟将接收所述报文的第一个比特的时刻生成硬件时间戳,将所述硬件时间戳和提取出的报文打包生成新的报文格式得到新格式报文;

1.4)解析标准时钟源输出的光IRIG-B码,获取所述光IRIG-B码的秒沿;

1.5)搜索所述新格式报文中的0标号报文,计算所述新格式报文中的0标号报文的第一个比特的时间、所述光IRIG-B码的秒沿之间的差值,得到被测合并单元输出的每一帧0标号报文的第一个比特的时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移。

3.根据权利要求2所述的用于智能变电站合并单元的守时误差检测方法,其特征在于,所述步骤1.4)中还包括如下同步本地时间的步骤:

1.4.1)连续扫描所述光IRIG-B码的码元,获取两个连续“P码”中第2个“P码”的上升沿作为光IRIG-B码的秒沿;

1.4.2)将本地时间的秒脉冲与所述光IRIG-B码的秒沿进行同步,实现本地时间与标准时钟源的秒时刻严格对齐。

4.根据权利要求3所述的用于智能变电站合并单元的守时误差检测方法,其特征在于:所述步骤1.2)中解析并提取出的报文具体是指基于IEC61850-9-2规约的SV报文。

5.根据权利要求4所述的用于智能变电站合并单元的守时误差检测方法,其特征在于:所述步骤1.3)中硬件时间戳为64位高精度时间戳。

6.根据权利要求5所述的用于智能变电站合并单元的守时误差检测方法,其特征在于:所述标准时钟源为GPS或北斗时钟源。

说明书

技术领域

本发明涉及电力系统智能变电站合并单元(MU)的测试技术,具体涉及一种用于智能变电站合并单元的守时误差检测方法。

背景技术

智能变电站采用电子式、光纤式或磁光玻璃式互感器采集电压电流信号,采用采集器或远端采集模块实现信号的接地采集与数字化,通过光纤及光数字报文将信号传输给合并单元,合并单元对多路采集信号进行合并,按IEC61850-9-2规约输出采样值SV(Sampled Value)报文给智能电子设备(以下简称IED设备)。对于采用传统电磁互感器的智能变电站,合并单元安装于户外开关场,采集电压电流互感器二次侧输出的电压电流模拟信号,合并后按IEC61850-9-2规约输出采样值的SV报文。

守时误差是合并单元的一项重要指标,在基于网络模式的智能变电站中,变电站同步是基于IEC61850-9-2规约的报文中的计数标号,报文虽经过交换机或网络传输具有不同的延时,但接收报文的IED设备按计数中的标号统一对齐,从而实现全网的SV报文同步。因此,要求在合并单元采样时需报文同步,一般做法是在IRIG-B码(InterRange Instrumentation Group美国靶场仪器组B型码)的秒沿时刻同步合并单元采样的0标号报文,秒与秒之间等间隔采样,对于4kHz采样率采样报文中的采样标号SmpCnt从0至3999翻转。

网络模式的智能变电站要求跨间隔的保护如变压器保护、母线保护等,在时钟同步信号短时间丢失时仍应具有一定的保护功能,按采样标号对齐的差动保护不能因SV报文的同步性变差而误动作。其它IED设备,如同步相量测量装置(PMU)等也是基于全网同步而工作的,因此,要求合并单元在时钟同步信号丢失后应具有一定的守时能力,根据Q-GDW426-2010《智能变电站合并单元技术规范》,合并单元在失去同步时钟信号10min以内的守时误差应小于4us,此项指标也是合并单元在型式试验及各种检测时必须进行的重要项目。

如图1所示,图1是目前通常采用的基于秒脉冲的合并单元守时误差检测方法,该方法要求合并单元具有秒脉冲输出接口,输出秒脉冲至时钟测试仪,通过比较两个1PPS的秒沿进行测试。标准时钟源同时向被测合并单元、GPS时钟测试仪输出光IRIG-B码,被测合并单元则通过秒脉冲(1PPS)接口向GPS时钟测试仪输出1PPS脉冲,GPS时钟测试仪则通过检测合并单元秒脉冲输出精度来获得合并单元的守时误差。但是,这种检测方法存在的问题主要有:(1)、要求合并单元有秒脉冲输出接口。但是目前各厂家的合并单元并不一定都有秒脉冲输出接口,因此无法输出秒脉冲信号供守时误差测试用。(2)、合并单元秒脉冲误差只能间接地反映守时对报文同步的影响,从严格意义上来讲,合并单元守时误差最终应反映到报文上,IED设备接收的是合并单元输出的SV报文,报文同步误差才直接影响到SV接收的性能,但报文的守时误差与合并单元秒脉冲输出精度之间无必然的联系。因此,通过检测合并单元秒脉冲输出精度来获得合并单元的守时误差必然存在检测准确度不直接的缺点。

发明内容

本发明要解决的技术问题是:针对现有技术的上述技术问题,提供一种能够直接测试合并单元报文守时误差,守时误差检测直接、准确性高、简单可靠、应用范围广泛的用于智能变电站合并单元的守时误差检测方法。

为了解决上述技术问题,本发明采用的技术方案为:

一种用于智能变电站合并单元的守时误差检测方法,步骤包括:

1)通过标准时钟源向被测合并单元输出光IRIG-B码并开始计时,获取接收到被测合并单元输出的每一帧0标号报文的第一个比特时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移△T1,在指定的计时时间内找出所述时间偏移的最小值△T1min;

2)保持标准时钟源的光IRIG-B码输出、拔掉被测合并单元的光IRIG-B码输入并开始计时,获取接收到被测合并单元输出的每一帧0标号报文第一个比特的时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移△T2,在指定的计时时间内找出所述时间偏移的最大值△T2max;

3)将所述最大值△T2max减去最小值△T1min,得到指定的计时时间内被测合并单元的守时误差△Tm。

优选地,所述步骤1)和步骤2)中获取接收到被测合并单元输出的每一帧0标号报文的第一个比特时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移的详细步骤包括:

1.1)接收被测合并单元输出的每一个报文帧;

1.2)解析并提取出所述接收报文帧中的报文;

1.3)根据本地的时钟将接收所述报文的第一个比特的时刻生成硬件时间戳,将所述硬件时间戳和提取出的报文打包生成新的报文格式得到新格式报文;

1.4)解析标准时钟源输出的光IRIG-B码,获取所述光IRIG-B码的秒沿;

1.5)搜索所述新格式报文中的0标号报文,计算所述新格式报文中的0标号报文的第一个比特的时间、所述光IRIG-B码的秒沿之间的差值,得到被测合并单元输出的每一帧0标号报文的第一个比特的时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移。

优选地,所述步骤1.4)中还包括如下同步本地时间的步骤:

1.4.1)连续扫描所述光IRIG-B码的码元,获取两个连续“P码”中第2个“P码”的上升沿作为光IRIG-B码的秒沿;

1.4.2)将本地时间的秒脉冲与所述光IRIG-B码的秒沿进行同步,实现本地时间与标准时钟源的秒时刻严格对齐。

优选地,所述步骤1.2)中解析并提取出的报文具体是指基于IEC61850-9-2规约的SV报文。

优选地,所述步骤1.3)中硬件时间戳为64位高精度时间戳。

优选地,所述标准时钟源为GPS或北斗时钟源。

本发明用于智能变电站合并单元的守时误差检测方法具有下述优点:

1、本发明不测量合并单元输出秒脉冲相对于绝对秒时刻偏移,而是通过接收合并单元输出的报文,获取接收到被测合并单元输出的每一帧0标号报文的第一个比特的时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移,比较有同步时钟信号及失去同步同步信号下接收到被测合并单元输出的每一帧0标号报文的第一个比特的时间与绝对秒时刻时间偏移,从而计算得到合并单元守时误差,该方法直接测量报文的守时误差,所测结果更能反映合并单元守时误差对报文接收智能电子设备的影响,具有守时误差检测直接、准确性高、检测方便快捷的优点。

2、本发明获取接收到被测合并单元输出的每一帧0标号报文的第一个比特的时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移,比较有同步时钟信号及失去同步同步信号下接收到被测合并单元输出的每一帧0标号报文的第一个比特的时间与绝对秒时刻的时间偏移,因此不要求被测合并单元有秒脉冲(1PPS)输出接口,而是直接使用被测合并单元输出报文,对于输出报文而言,被测合并单元的前端不需要施加电压电流的模拟量或数字量,只需要被测合并单元接时钟同步信号并有报文输出即可,该检测方法简单可靠,具有很强的工程实用性。

3、本发明获取接收到被测合并单元输出的每一帧0标号报文的第一个比特的时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移,比较有同步时钟信号及失去同步同步信号下接收到被测合并单元输出的每一帧0标号报文的第一个比特的时间与绝对秒时刻时间偏移,因此不要求被测合并单元有秒脉冲(1PPS)输出接口,能够适用于各类不具有秒脉冲(1PPS)输出接口的合并单元的守时误差检测,具有应用范围广的优点。

附图说明

图1为现有技术基于GPS时钟测试仪的守时误差检测系统结构示意图。

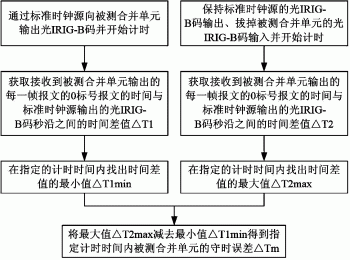

图2为本发明实施例方法的实施步骤示意图。

图3为本发明实施例方法中检测时间偏移的原理示意图。

图4为应用本发明实施例方法的合并单元守时误差检测装置的框架结构示意图。

图5为应用本发明实施例方法的合并单元守时误差检测装置的连接结构示意图。

图6为应用本发明实施例方法的合并单元守时误差检测装置的FPGA框架结构示意图。

具体实施方式

如图2所示,本实施例用于智能变电站合并单元的守时误差检测方法的步骤包括:

1)通过标准时钟源向被测合并单元输出光IRIG-B码并开始计时,获取接收到被测合并单元输出的每一帧0标号报文的第一个比特时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移△T1,在指定的计时时间内找出时间偏移的最小值△T1min;

2)保持标准时钟源的光IRIG-B码输出、拔掉被测合并单元的光IRIG-B码输入并开始计时,获取接收到被测合并单元输出的每一帧0标号报文的第一个比特时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移△T2,在指定的计时时间内找出时间偏移的最大值△T2max;

3)将最大值△T2max减去最小值△T1min,得到指定的计时时间内被测合并单元的守时误差△Tm。

如图3所示,本实施例步骤1)每接收到每一帧报文,则搜索0标号报文,计算接收0标号报文的第一个比特的时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移△T1,在指定的计时时间内找出时间偏移△T1的最小值△T1min;本实施例步骤2)每接收到每一帧报文,则搜索0标号报文,计算接收0标号报文的第一个比特的时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移△T2,在指定的计时时间内找出时间偏移△T2的最大值△T2max;最终,将最大值△T2max减去最小值△T1min得到被测合并单元的守时误差△Tm。本实施例中,指定的计时时间为10min,从而能够快速判断处合并单元在失去同步时钟信号10min以内的守时误差是否小于4us,此项指标也是合并单元在型式试验及各种检测时的重要项目。

本实施例中,步骤1)和步骤2)中获取接收到被测合并单元输出的每一帧0标号报文的第一个比特时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移的详细步骤包括:

1.1)接收被测合并单元输出的每一个报文帧;

1.2)解析并提取出接收报文帧中的报文;

1.3)根据本地的时钟将接收报文的第一个比特的时刻生成硬件时间戳,将硬件时间戳和提取出的报文打包生成新的报文格式;本实施例中,采用FPGA对接收报文打上硬件时间戳,且打上硬件时间戳的时间分辨率为10ns;

1.4)解析标准时钟源输出的光IRIG-B码,获取光IRIG-B码的秒沿;

1.5)搜索新格式报文中的0标号报文,计算新格式报文中的0标号报文的第一个比特的时间、光IRIG-B码的秒沿之间的差值,得到被测合并单元输出的每一帧0标号报文的第一个比特的时间与标准时钟源输出的光IRIG-B码秒沿之间的时间偏移。

本实施例中,步骤1.4)中还包括如下同步本地时间的步骤:

1.4.1)连续扫描所述光IRIG-B码的码元,获取两个连续“P码”中第2个“P码”的上升沿作为光IRIG-B码的秒沿;

1.4.2)将本地时间的秒脉冲与光IRIG-B码的秒沿进行同步,实现本地时间与标准时钟源的秒时刻严格对齐。

本实施例通过上述步骤1.4.1)~1.4.2)同步本地时间,确保在检测时本地时间与标准时钟源的秒时刻严格对齐,从而能够提升守时误差检测的精确度。

步骤1.2)中解析并提取出的报文具体是指基于IEC61850-9-2规约的SV报文。本实施例中,步骤1.2)中解析并提取出的报文具体是指基于IEC61850-9-2规约的SV报文,在合并单元的同步信号(光IRIG-B码)存在情况下,测量SV报文的0标号报文与光IRIG-B码的秒沿的时间偏差△T1,比较计算△T1的最小值△T1min,在合并单元的同步信号丢失情况下,测量SV报文的0标号报文与秒沿时间偏差△T2,在可设置的间隔时间内,比较计算△T2的最大值△T2max,计算△Tm=T2max-T1max,即为合并单元在相应时间内的守时误差。

本实施例中,步骤1.3)中硬件时间戳为64位高精度时间戳,精确度高,能够提升守时误差检测的精确度。

本实施例中,标准时钟源为GPS或北斗时钟源。标准时钟源通过卫星天线接收GPS或北斗卫星的授时,相比于本地时钟电路而言具有精确度高的优点。

如图4所示,应用本实施例用于智能变电站合并单元的守时误差检测方法的合并单元守时误差检测装置采用DSP+ARM+FPGA架构。除了DSP+ARM+FPGA三个核心模块以外,该装置还包括LCD、按键模块、SD卡、FLASH、DRAM以及光IRIG-B码接口、100BASE-FX接口,其光IRIG-B码接口、100BASE-FX接口分别与FPGA芯片相连,DSP采用两条总线(高速总线及低延迟总线)与FPGA交换数据,并执行数据的缓存、搜索、计算等功能。ARM运行Linux操作系统,采用QT进行应用程序开发,执行与底层DSP的通讯与数据交互、界面的设置与显示、数据的导出等功能。如图5所示,该合并单元守时误差检测装置具有单纤功能,支持采用单根光纤将合并单元连接至100BASE-FX接口的接收口RX上,接收被测试合并单元发送的报文,同时通过光IRIG-B码接口接收标准时钟源的光IRIG-B码,此外标准时钟源还为被测试的合并单元提供光IRIG-B码;此外合并单元守时误差检测装置采用锂电池供电,自带液晶及键盘,具有操作、携带方便的特点。

如图6所示,FPGA包括有以太网MAC模块、GOOSE(Generic Object Oriented Substation Event,面向对象的变电站通用事件)/SV报文识别模块、时间戳生成模块、光IRIG-B码解码模块、高速总线接口控制模块、低延迟总线接口控制模块,其以太网MAC模块与FPGA外部的100BASE-FX接口相连,光IRIG-B码解码模块则与FPGA外部的光IRIG-B码接口相连。FPGA中各个模块的功能如下:

以太网MAC模块,用于通过100BASE-FX接口接收被测合并单元输出的每一个报文帧,并将其存放在DRAM中。

低延迟总线接口控制模块,用于接收FPGA外部的CPU的命令,控制GOOSE/SV报文识别模块解析并提取出报文帧中的SV报文;外部的CPU通过低延迟总线控制低延迟总线接口控制模块,低延迟总线接口控制模块控制GOOSE/SV报文识别模块分析以太网MAC模块解析出来的报文,从中提取出SV报文;

时间戳生成模块,用于根据本地的100MHZ时钟将接收报文的包头的时刻生成64位高精度的硬件时间戳,将接收到SV报文的硬件时间戳和提取出的报文(从DRAM中读取)打包生成新的报文格式,并将其存放在DRAM中。此外,时间戳生成模块根据光IRIG-B码的秒沿,让本地时间的PPS与标准IRIG-B(即光IRIG-B码的秒沿对齐,实现秒时刻的严格对齐。

高速总线接口控制模块,用于从DRAM中读取新的报文,以高速总线时序通过总线传输给外部CPU;外部CPU获得新报文,进行分析。

光IRIG-B码解码模块,用于解析标准时钟源输出的光IRIG-B码,获取光IRIG-B码的时间(IRIG-B时间),外部CPU会通过低延迟总线读取IRIG-B时间信息;同时,光IRIG-B码解码模块还获得光IRIG-B码的秒沿,即,获取码元中两个连续“P码”,第2个“P码”的上升沿,时间戳生成模块根据光IRIG-B码的秒沿(irig_b时间)及本地的秒脉冲PPS实现秒时刻的严格对齐。

最终,外部CPU比较有同步时钟信号及失去同步同步信号下接收到被测合并单元输出的每一帧报文的0标号报文的时间与绝对秒时刻的时间偏移,从而计算得到合并单元守时误差,该方法直接测量报文的守时误差,所测结果更能反映合并单元守时误差对报文接收智能电子设备的影响,具有守时误差检测准确性高、检测方便快捷的优点。

以上所述仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

一种用于智能变电站合并单元的守时误差检测方法专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0