IPC分类号 : H01L21/822,G01R31/28,H01L21/66,H01L25/065,H01L25/07,H01L25/18,H01L27/00,H01L27/04

专利摘要

在相互层叠的集成电路层(10)及(20),分别形成多个检查用整流元件部(15)及(25)。多个检查用整流元件部(15)((25))连接于多个连接用端子(14)((24))的各个与正电源配线(13a)((23a))及接地配线(13b)((23b))之间,包含整流元件(15a、15b)((25a、25b))并通过电流而发光。将多个连接用端子(14)及(24)相互电连接之后,在正电源配线(13a)(或接地配线(13b))与接地配线(23b)(或正电源配线(23a))之间施加偏压,根据检查用整流元件部(15)或(25)的发光,检查连接用端子(14)及(24)的连接状态。由此,可以每层叠一层便在短时间内检查在厚度方向上层叠多个集成电路层而成的半导体集成电路装置的层间连接不良的有无。

权利要求

1.一种半导体集成电路装置的检查方法,其特征在于,

其是检查在厚度方向上层叠多个集成电路层而成的半导体集成电路装置的方法,该多个集成电路层分别包含具有表面及背面的支撑层、以及形成于该支撑层的所述表面的半导体元件组及配线,

在制作一个所述集成电路层时,在所述表面形成多个第1检查用整流元件部,该多个第1检查用整流元件部连接于用于电连接于另一个所述集成电路层的多个连接用端子的各个与所述配线之间、且包含整流元件并通过电流而发光,

在制作所述另一个集成电路层时,在所述表面形成多个第2检查用整流元件部,该多个第2检查用整流元件部连接于用于电连接于所述一个集成电路层的多个连接用端子的各个与所述配线之间、且包含整流元件并通过电流而发光,

在将所述一个集成电路层与所述另一个集成电路层相互层叠时,使该另一个集成电路层的所述表面与所述一个集成电路层相对,

将所述一个集成电路层的所述多个连接用端子与所述另一个集成电路层的所述多个连接用端子相互电连接之后,经由所述一个所述集成电路层的所述配线与所述另一个所述集成电路层的所述配线而对所述第1及第2检查用整流元件部施加偏压,

根据在所述另一个集成电路层的所述背面侧所观察的所述第1及第2检查用整流元件部中的至少一者的发光,检查所述一个集成电路层的所述多个连接用端子与所述另一个集成电路层的所述多个连接用端子的连接状态。

2.如权利要求1所述的半导体集成电路装置的检查方法,其特征在于,

所述第1及第2检查用整流元件部还包含与所述整流元件串联连接的发光元件。

3.如权利要求1所述的半导体集成电路装置的检查方法,其特征在于,

所述第1及第2检查用整流元件部的所述整流元件通过电流而发光。

4.如权利要求1至3中任一项所述的半导体集成电路装置的检查方法,其特征在于,

在所述一个集成电路层及所述另一个集成电路层的至少一者,还形成通过来自该半导体集成电路装置的外部的能量输入而产生所述偏压的电压施加部。

5.如权利要求4所述的半导体集成电路装置的检查方法,其特征在于,

所述电压施加部包含通过自该半导体集成电路装置的外部所照射的光而产生电动势的光电转换元件。

6.如权利要求1至5中任一项所述的半导体集成电路装置的检查方法,其特征在于,

所述一个集成电路层的所述配线是为了将电源电压供给至所述半导体元件组而形成于所述支撑层的所述表面上的正电源配线及接地配线中的一方的配线,

所述另一个集成电路层的所述配线是为了将电源电压供给至所述半导体元件组而形成于所述支撑层的所述表面上的正电源配线及接地配线中的另一方的配线,

在制作所述一个集成电路层时,相对于所述一方的配线反方向地连接所述多个第1检查用整流元件部的所述整流元件,

在制作所述另一个集成电路层时,相对于所述另一方的配线反方向地连接所述多个第2检查用整流元件部的所述整流元件。

7.如权利要求1至5中任一项所述的半导体集成电路装置的检查方法,其特征在于,

所述多个集成电路层的所述配线与所述半导体元件组独立地设置且用于检查。

8.一种半导体集成电路装置,其特征在于,

其是在厚度方向上层叠多个集成电路层而成的半导体集成电路装置,该多个集成电路层分别包含具有表面及背面的支撑层、以及形成于该支撑层的所述表面的半导体元件组及配线,

一个所述集成电路层包含:

多个连接用端子,其用于电连接于另一个所述集成电路层;及

多个第1检查用整流元件部,其形成于所述表面,连接于所述多个连接用端子的各个与所述配线之间,包含整流元件且通过电流而发光,

所述另一个集成电路层包含:

多个连接用端子,其用于电连接于所述一个集成电路层;及

多个第2检查用整流元件部,其形成于所述表面,连接于所述多个连接用端子的各个与所述配线之间,包含整流元件且通过电流而发光,

所述另一个集成电路层的所述表面与所述一个集成电路层相互相对,

所述一个集成电路层的所述多个连接用端子与所述另一个集成电路层的所述多个连接用端子相互电连接,

还包含经由所述一个所述集成电路层的所述配线与所述另一个所述集成电路层的所述配线而对所述第1及第2检查用整流元件部施加偏压的电压施加部。

9.如权利要求8所述的半导体集成电路装置,其特征在于,

所述第1及第2检查用整流元件部还包含与所述整流元件串联连接的发光元件。

10.如权利要求8所述的半导体集成电路装置,其特征在于,

所述第1及第2检查用整流元件部的所述整流元件通过电流而发光。

11.如权利要求8至10中任一项所述的半导体集成电路装置,其特征在于,

所述电压施加部设置于一个集成电路层及所述另一个集成电路层的至少一者,通过来自该半导体集成电路装置的外部的能量输入而产生所述偏压。

12.如权利要求11所述的半导体集成电路装置,其特征在于,

所述电压施加部包含通过自该半导体集成电路装置的外部所照射的光而产生电动势的光电转换元件。

13.如权利要求8至12中任一项所述的半导体集成电路装置,其特征在于,

所述一个集成电路层的所述配线是为了将电源电压供给至所述半导体元件组而形成于所述支撑层的所述表面上的正电源配线及接地配线中的一方的配线,

所述另一个集成电路层的所述配线是为了将电源电压供给至所述半导体元件组而形成于所述支撑层的所述表面上的正电源配线及接地配线中的另一方的配线,

所述多个第1检查用整流元件部的所述整流元件相对于所述一方的配线反方向地连接,

所述多个第2检查用整流元件部的所述整流元件相对于所述另一方的配线反方向地连接。

14.如权利要求8至12中任一项所述的半导体集成电路装置,其特征在于,

所述多个集成电路层的所述配线与所述半导体元件组独立地设置且用于检查。

说明书

技术领域

本发明涉及半导体集成电路装置的检查方法及半导体集成电路装置。

背景技术

在专利文献1中,公开有具有将母芯片与子芯片接合而成的所谓的芯片内建芯片(chip-on-chip)构造的半导体装置。母芯片及子芯片的电源部及接地部电性分离。在各芯片的接地配线与信号配线之间及电源配线与信号配线之间反方向地连接有二极管(保护二极管或寄生二极管)。检查信号连接凸块间的接合的好坏时,分别使测试探针接触母芯片的信号连接凸块与用于将接地电位供给至子芯片的接地连接凸块而施加检查电压,检查是否形成有经由二极管的电路。

在专利文献2中,公开有与层叠多个芯片而构成的层叠模块相关的技术。该层叠模块包含所层叠的多个芯片与配置于该多个芯片的下方的基板。各芯片在其上表面包含安装用焊垫及检查用导通焊垫,在其下表面包含安装用端子、与检查用导通焊垫电连接的检查用导通端子、及与检查用导通端子邻接的检查信号用端子。在基板的上表面配置有与芯片下表面的检查用导通端子接合的检查用接合部,在基板的下表面配置有安装用端子及检查用导通端子。在该层叠模块中,将已安装的芯片的检查用焊垫与层叠的芯片的检查用端子接合,自与检查用焊垫电性导通的已安装的芯片的检查用端子输入检查用信号进行导通检查。

在专利文献3中,公开有与分别包含多个存储器模块作为存储器子系统的存储器系统相关的技术。该存储器系统包含层叠于IO芯片上的多个DRAM(Dynamic Random Access Memory,动态随机存储器)芯片与将各DRAM芯片与IO芯片连接的贯通电极,在IO芯片中将系统数据信号与各DRAM芯片内的内部数据信号相互转换。

在专利文献4中,公开有与根据利用发光显微镜等检测出的反应部位推断作为反应的主要原因的不良位置的CAD工具等程序及使用其的不良分析方法相关的技术。在该不良分析方法中,通过检测形成于电路内的晶体管的发光,从而限定电路的故障部位。

专利文献

专利文献1:日本特开2001-135778号公报

专利文献2:日本特开2004-281633号公报

专利文献3:日本特开2004-327474号公报

专利文献4:日本特开2003-86689号公报

发明内容

发明所要解决的问题

目前,半导体集成电路的微细化技术已明显进步,但进一步微细化逐渐变得困难。因此,为了进一步提高电路的集成密度,正在开发在厚度方向上层叠多个形成有集成电路的基板或层而成的半导体集成电路装置。该半导体集成电路装置因必需在多个集成电路层间进行信号的授受,因而在各集成电路层之间包含凸块电极等的电连接用端子。

在如此的半导体集成电路装置中,各集成电路层的集成电路规模越大,用于将集成电路层彼此连接的连接用端子的数量越多。因此,产生连接不良的机率增大,因此,对连接用端子的导通检查必不可少。尤其,若可以每层叠一层便进行导通检查,则可有效地防止在具有连接不良部位的集成电路层上层叠新的集成电路层的徒劳。

然而,在如例如专利文献1中所公开的方法那样针对每个连接用端子进行探测的方法中,在半导体集成电路装置包含多个连接用端子的情况下检查需要很长时间与工夫。另外,有因探测而在焊垫表面产生损伤或污垢,从而产生连接不良的担忧,因此难以应用于每层叠一层便进行导通检查的连续式检查。

本发明的目的在于提供一种可以每层叠一层便在短时间内检查在厚度方向上层叠多个集成电路层而成的半导体集成电路装置的层间连接不良的有无的检查方法及半导体集成电路装置。

解决问题的技术手段

本发明的一个实施方式所涉及的半导体集成电路装置的检查方法的特征在于:其是检查在厚度方向上层叠分别包含具有表面及背面的支撑层、与形成于该支撑层的表面的半导体元件组及配线的多个集成电路层而成的半导体集成电路装置的方法,在制作一个集成电路层时,在表面形成连接于用于电连接于另一个集成电路层的多个连接用端子的各个与配线之间、且包含整流元件并通过电流而发光的多个第1检查用整流元件部;在制作另一个集成电路层时,在表面形成连接于用于电连接于一个集成电路层的多个连接用端子的各个与配线之间、且包含整流元件并通过电流而发光的多个第2检查用整流元件部;在将一个集成电路层与另一个集成电路层相互层叠时,使该另一个集成电路层的表面与一个集成电路层相对;将一个集成电路层的多个连接用端子与另一个集成电路层的多个连接用端子相互电连接之后,经由一个集成电路层的配线与另一个集成电路层的配线而对第1及第2检查用整流元件部施加偏压;根据在另一个集成电路层的背面侧所观察的第1及第2检查用整流元件部的发光,检查一个集成电路层的多个连接用端子与另一个集成电路层的多个连接用端子的连接状态。

在该半导体集成电路装置的检查方法中,在制作一个集成电路层时,将第1检查用整流元件部连接于多个(层间)连接用端子的各个与配线之间。同样地,在制作另一个集成电路层时,将第2检查用整流元件部连接于多个(层间)连接用端子的各个与配线之间。这些第1及第2检查用整流元件部包含整流元件,接受电流的供给而发光。再者,在检查用整流元件部中,整流元件本身也可发光,与整流元件分开设置的发光元件也可发光。

而且,通过例如凸块等将上述一个集成电路层的多个连接用端子与上述另一个集成电路层的多个连接用端子相互电连接之后,经由一个集成电路层的配线与另一个集成电路层的配线,对第1及第2检查用整流元件部施加偏压。此时,在一个集成电路层的连接用端子与另一个集成电路层的连接用端子良好地连接的情况下,构成一个集成电路层的配线~第1检查用整流元件部~一个集成电路层的连接用端子~另一个集成电路层的连接用端子~第2检查用整流元件部~另一个集成电路层的配线的电流路径,因此,第1及第2检查用整流元件部发光。然而,在一个集成电路层的连接用端子与另一个集成电路层的连接用端子产生连接不良的情况下,上述电流路径在连接用端子间被切断,因此第1及第2检查用整流元件部不发光或未达到规定的发光量。

即,根据上述的半导体集成电路装置的检查方法,根据第1及第2检查用整流元件部中的至少一者的发光,可检查一个集成电路层的多个连接用端子与另一个集成电路层的多个连接用端子的连接状态。因此,通过总括观察与多个连接用端子的各个对应的发光的有无,可容易地判断连接不良的有无,从而可以每层叠一层集成电路层便在短时间内检查连接不良的有无。

另外,半导体集成电路装置的检查方法的特征也在于:第1及第2检查用整流元件部还包含与整流元件串联连接的发光元件。或者,半导体集成电路装置的检查方法的特征也在于:第1及第2检查用整流元件部的整流元件通过电流而发光。通过其中的任一构成,可良好地实现上述的第1及第2检查用整流元件部。

另外,半导体集成电路装置的检查方法的特征也在于:进而在一个集成电路层及另一个集成电路层的至少一者形成通过来自该半导体集成电路装置的外部的能量输入而产生偏压的电压施加部。由此,不用利用探测进行偏压的施加,因此可进一步减少检查时的探测次数(或不进行探测)。在此情况下,电压施加部也可包含通过自该半导体集成电路装置的外部所照射的光而产生电动势的光电转换元件。由此,可良好地实现电压施加部。

另外,半导体集成电路装置的检查方法的特征也在于:一个集成电路层的配线是为了将电源电压供给至半导体元件组而形成于支撑层的表面上的正电源配线及接地配线中的一方的配线;另一个集成电路层的配线是为了将电源电压供给至半导体元件组而形成于支撑层的表面上的正电源配线及接地配线中的另一方的配线;在制作一个集成电路层时,相对于一方的配线反方向地连接多个第1检查用整流元件部的整流元件;在制作另一个集成电路层时,相对于另一方的配线反方向地连接多个第2检查用整流元件部的整流元件。

在该检查方法中,因在一个集成电路层中,相对于正电源配线及接地配线中的一方的配线反方向地连接第1检查用整流元件部的整流元件,因而在通常的动作时电流未流至第1检查用整流元件部。同样地,因在另一个集成电路层中,相对于正电源配线及接地配线中的另一方的配线反方向地连接第2检查用整流元件部的整流元件,因而在通常的动作时电流也未流至第2检查用整流元件部。然后,在检查时,在一个集成电路层的上述一方的配线与另一个集成电路层的上述另一方的配线之间,对第1及第2检查用整流元件部施加成为正向(即,与通常的动作时的电源电压正负相反)的检查用电压,由此可将电流供给至第1及第2检查用整流元件部而使其发光。因此,根据该检查方法,可利用既存的电源配线及接地配线检查层间连接不良的有无。其中,多个集成电路层的配线也可为与半导体元件组独立地设置且用于检查的配线。

本发明的半导体集成电路装置的特征在于:其是在厚度方向上层叠分别包含具有表面及背面的支撑层、与形成于该支撑层的表面的半导体元件组及配线的多个集成电路层而成的半导体集成电路装置,一个集成电路层包含:多个连接用端子,其用于电连接于另一个集成电路层;及多个第1检查用整流元件部,其形成于表面,连接于多个连接用端子的各个与配线之间,且包含整流元件并通过电流而发光;另一个集成电路层包含:多个连接用端子,其用于电连接于一个集成电路层;及多个第2检查用整流元件部,其形成于表面,连接于多个连接用端子的各个与配线之间,且包含整流元件并通过电流而发光;另一个集成电路层的表面与一个集成电路层相互相对,一个集成电路层的多个连接用端子与另一个集成电路层的多个连接用端子相互电连接,且还包含经由一个集成电路层的配线与另一个集成电路层的配线而对第1及第2检查用整流元件部施加偏压的电压施加部。

在该半导体集成电路装置中,一个集成电路层包含连接于多个(层间)连接用端子的各个与配线之间的第1检查用整流元件部。同样地,另一个集成电路层包含连接于多个(层间)连接用端子的各个与配线之间的第2检查用整流元件部。这些第1及第2检查用整流元件部包含整流元件,接受电流的供给而发光。

而且,上述一个集成电路层的多个连接用端子与上述另一个集成电路层的多个连接用端子通过例如凸块等而相互电连接。进而,电压施加部经由一个集成电路层的配线与另一个集成电路层的配线对第1及第2检查用整流元件部施加偏压。此时,在一个集成电路层的连接用端子与另一个集成电路层的连接用端子良好地连接的情况下,如上述的检查方法中所说明的那样,第1及第2检查用整流元件部会发光。然而,在一个集成电路层的连接用端子与另一个集成电路层的连接用端子产生连接不良的情况下,第1及第2检查用整流元件部不发光。

即,根据上述的半导体集成电路装置,根据第1及第2检查用整流元件部中的至少一者的发光,可检查一个集成电路层的多个连接用端子与另一个集成电路层的多个连接用端子的连接状态。因此,通过总括观察与多个连接用端子的各个对应的发光的有无,可容易地判断连接不良的有无,从而可以每层叠一层集成电路层便在短时间内检查连接不良的有无。

另外,半导体集成电路装置的特征也在于:第1及第2检查用整流元件部还包含与整流元件串联连接的发光元件。或者,半导体集成电路装置的特征也在于:第1及第2检查用整流元件部的整流元件通过电流而发光。通过其中的任一构成,可良好地实现上述的第1及第2检查用整流元件部。

另外,半导体集成电路装置的特征也在于:电压施加部设置于一个集成电路层及另一个集成电路层的至少一者,通过来自该半导体集成电路装置的外部的能量输入而产生偏压。由此,不用利用探测进行偏压的施加,因此可进一步减少检查时的探测次数(或不进行探测)。在此情况下,电压施加部也可包含通过自该半导体集成电路装置的外部所照射的光而产生电动势的光电转换元件。由此,可良好地实现电压施加部。

另外,半导体集成电路装置的特征也在于:一个集成电路层的配线是为了将电源电压供给至半导体元件组而形成于支撑层的表面上的正电源配线及接地配线中的一方的配线,另一个集成电路层的配线是为了将电源电压供给至半导体元件组而形成于支撑层的表面上的正电源配线及接地配线中的另一方的配线,多个第1检查用整流元件部的整流元件相对于一方的配线反方向地连接,多个第2检查用整流元件部的整流元件相对于另一方的配线反方向地连接。

在该半导体集成电路装置中,因在一个集成电路层中,第1检查用整流元件部的整流元件相对于正电源配线及接地配线中的一方的配线反方向地连接,因而在通常的动作时电流未流至第1检查用整流元件部。同样地,因在另一个集成电路层中,第2检查用整流元件部的整流元件相对于正电源配线及接地配线中的另一方的配线反方向地连接,因而在通常的动作时电流也未流至第2检查用整流元件部。而且,在检查时,在一个集成电路层的上述一方的配线与另一个集成电路层的上述另一方的配线之间,对第1及第2检查用整流元件部施加成为正向(即,与通常的动作时的电源电压正负相反)的检查用电压,由此可将电流供给至第1及第2检查用整流元件部而使其发光。因此,根据该半导体集成电路装置,可利用既存的电源配线及接地配线检查层间连接不良的有无。其中,多个集成电路层的配线也可为与半导体元件组独立地设置且用于检查的配线。

发明的效果

根据本发明,可以每层叠一层便在短时间内检查在厚度方向上层叠多个集成电路层而成的半导体集成电路装置的层间连接不良的有无。

附图说明

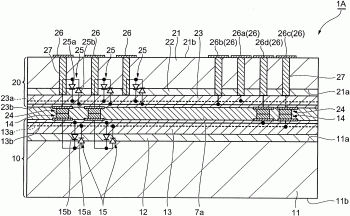

图1是表示本发明所涉及的半导体集成电路装置的第1实施方式的构成的剖面图。

图2是表示检查用整流元件部的构成的图。

图3是表示半导体集成电路装置的检查方法的流程图。

图4是表示检查用整流元件部的构成的图。

图5是表示检查用整流元件部的构成的图。

图6是表示检查用整流元件部的构成的图。

图7是表示作为第2实施方式的半导体集成电路装置的构成的剖面图。

图8是表示作为第3实施方式的半导体集成电路装置的构成的剖面图。

图9是表示作为第4实施方式的半导体集成电路装置的构成的剖面图。

图10是表示作为第5实施方式的半导体集成电路装置的构成的剖面图。

图11是表示作为第6实施方式的半导体集成电路装置的构成的剖面图。

图12是表示作为第7实施方式的半导体集成电路装置的构成的剖面图。

图13是表示作为第8实施方式的电源配线及接地配线的构成的图。

图14是表示作为第9实施方式的电压施加部的构成的图。

图15是表示作为第10实施方式的检查装置的构成的图。

图16是表示作为第11实施方式的检查装置的构成的图。

具体实施方式

以下,参照附图,详细地说明本发明的半导体集成电路装置的检查方法及半导体集成电路装置的实施方式。再者,在附图的说明中对相同的要素附上相同的符号,并省略重复的说明。

(第1实施方式)

图1是表示半导体集成电路装置的第1实施方式的构成的剖面图。如图1所示,本实施方式的半导体集成电路装置1A通过在厚度方向上层叠第1集成电路层10与第2集成电路层20而成。再者,在本实施方式中,以集成电路层10所具有的半导体基板11的表面(器件形成面)11a与集成电路层20所具有的半导体基板21的表面(器件形成面)21a相互相对的方式,将集成电路层10、20相互接合。

集成电路层10包含具有表面11a及背面11b的半导体基板11、设置于半导体基板11的表面11a的器件层12、设置于器件层12上的配线层13、及用于电连接于集成电路层20的多个连接用端子(电极)14。同样地,集成电路层20包含具有表面21a及背面21b的半导体基板21、设置于半导体基板21的表面21a的器件层22、设置于器件层22上的配线层23、及用于电连接于集成电路层10的多个连接用端子(电极)24。

半导体基板11、21例如由硅构成。半导体基板11、21是集成电路层10、20的支撑层。器件层12、22含有例如由晶体管等多个半导体元件构成的半导体元件组。多个半导体元件在半导体基板11、21的表面11a、21a上经过离子植入等的半导体工艺而形成。再者,多个半导体元件也可通过在半导体基板11、21上磊晶(epitaxial)成长半导体晶体而形成。另外,多个半导体元件也可通过例如ALD(Atomic Layer Deposition,原子层沉积)等的未利用离子植入的半导体工艺而形成。

配线层13、23包含用于将器件层12、22中所包含的多个半导体元件相互电连接的多个配线。这些多个配线中除包含将半导体元件彼此连接的信号配线以外,也包含用于对多个半导体元件施加电源电压的正电源配线13a、23a及接地配线13b、23b。在本实施方式中,集成电路层10的正电源配线13a及接地配线13b、与集成电路层20的正电源配线23a及接地配线23b相互独立地配置,在检查时,未形成相互的连接。

多个连接用端子14、24分别设置于配线层13、23上。集成电路层10的多个连接用端子14各个与集成电路层20的多个连接用端子24各个配置于表面11a上及表面21a上相互相对的位置上,且通过相互接触而电连接。多个连接用端子14、24的各个通过例如凸块电极而良好地构成。

另外,集成电路层10进而包含多个第1检查用整流元件部15。多个检查用整流元件部15各个形成于器件层12,且与信号配线用的多个连接用端子14各个一对一地对应。多个检查用整流元件部15分别包含整流元件15a及15b。整流元件15a及15b例如为二极管。整流元件15a反方向连接于集成电路层10的正电源配线13a与连接用端子14之间,整流元件15b反方向连接于集成电路层10的接地配线13b与连接用端子14之间。更具体而言,整流元件15a的阴极与正电源配线13a相互连接,整流元件15a的阳极与连接用端子14相互连接。另外,整流元件15b的阳极与接地配线13b相互连接,整流元件15b的阴极与连接用端子14相互连接。再者,图1中为了容易理解,明示整流元件(二极管)15a、15b的电路符号。

检查用整流元件部15具有用于通过电流而发光的构成。如此的构成通过例如整流元件15a及15b本身通过电流发光而良好地实现。或者,检查用整流元件部15也通过进而包含分别与整流元件15a及15b串联连接的2个发光元件而良好地实现。

集成电路层20进而包含多个第2检查用整流元件部25。多个检查用整流元件部25各个形成于器件层22,且与信号配线用的多个连接用端子24各个一对一地对应。多个检查用整流元件部25分别包含整流元件25a及25b。整流元件25a及25b例如为二极管。整流元件25a反方向连接于集成电路层20的正电源配线23a与连接用端子24之间,整流元件25b反方向连接于集成电路层20的接地配线23b与连接用端子24之间。更具体而言,整流元件25a的阴极与正电源配线23a相互连接,整流元件25a的阳极与连接用端子24相互连接。另外,整流元件25b的阳极与接地配线23b相互连接,整流元件25b的阴极与连接用端子24相互连接。再者,图1中为了容易理解,明示整流元件(二极管)25a、25b的电路符号。

检查用整流元件部25具有用于通过电流而发光的构成。如此的构成通过例如整流元件25a及25b本身通过电流发光而良好地实现。或者,检查用整流元件部25也通过进而包含分别与整流元件25a及25b串联连接的2个发光元件而良好地实现。

此处,例示包含与整流元件串联连接的发光元件的检查用整流元件部。图2是表示检查用整流元件部35A的构成的图。该检查用整流元件部35A可与图1所示的检查用整流元件部15及25进行替换。

如图2所示,检查用整流元件部35A包含反方向连接于连接用端子14或24与正电源配线13a或23a之间的整流元件35a、与相对于该整流元件35a串联连接的作为发光元件的发光用二极管35c。另外,检查用整流元件部35A包含反方向连接于连接用端子14或24与接地配线13b或23b之间的整流元件35b、与相对于该整流元件35b串联连接的作为发光元件的发光用二极管35d。

再次参照图1。集成电路层20为了将半导体基板21的表面21a上的配线层23的配线与背面21b上的多个连接用端子(电极)26相互连接,进而包含多个贯通配线(Through Silicon Via:TSV)27。多个连接用端子26中的一个连接用端子26a经由贯通配线27而与集成电路层20的正电源配线23a电连接。多个连接用端子26中的一个连接用端子26b经由贯通配线27而与集成电路层20的接地配线23b电连接。多个连接用端子26中的一个连接用端子26c经由贯通配线27、连接用端子24及14而与集成电路层10的正电源配线13a电连接。多个连接用端子26中的一个连接用端子26d经由贯通配线27、连接用端子24及14而与集成电路层10的接地配线13b电连接。如此,在本实施方式中,为了相互独立地配设集成电路层10及20的电源系统,而设置有连接用端子26a~26d。连接用端子26a~26d及连接于它们的贯通配线27构成用于经由集成电路层10的正电源配线13a(或接地配线13b)与集成电路层20的接地配线23b(或正电源配线23a)对检查用整流元件部15、25施加偏压的电压施加部。

半导体集成电路装置1A进而包含粘结层7a。粘结层7a设置于集成电路层10与集成电路层20的间隙中,将集成电路层10及集成电路层20机械地接合。再者,该粘结层7a优选为含有可遮蔽来自检查用整流元件部15的光的材料。

对以上所说明的半导体集成电路装置1A的检查方法进行说明。图3是表示该检查方法的流程图。

首先,个别地制作集成电路层10及20的各个(集成电路层形成步骤S11)。具体而言,准备用于集成电路层10的半导体基板11,在半导体基板11的表面11a形成器件层12。此时,将半导体元件组与检查用整流元件部15(整流元件15a、15b)一并形成于器件层12。其次,在器件层12上形成配线层13。此时,将用于电连接于集成电路层20的多个连接用端子14、正电源配线13a及接地配线13b形成于配线层13的内部或配线层13上。另外,形成用于将整流元件15a连接于连接用端子14与正电源配线13a之间的配线、以及用于将整流元件15b连接于连接用端子14与接地配线13b之间的配线。再者,在该步骤S11中,优选通过进行集成电路层10的动作测试,预先检查器件层12的半导体元件组无异常。

集成电路层20也与集成电路层10同样地形成。即,准备用于集成电路层20的半导体基板21,在半导体基板21的表面21a形成器件层22。此时,将半导体元件组与检查用整流元件部25(整流元件25a、25b)一并形成于器件层22。其次,在器件层22上形成配线层23。此时,将用于电连接于集成电路层10的多个连接用端子24、正电源配线23a及接地配线23b形成于配线层23的内部或配线层23上。另外,形成用于将整流元件25a连接于连接用端子24与正电源配线23a之间的配线、以及用于将整流元件25b连接于连接用端子24与接地配线23b之间的配线。再者,在该步骤S11中,优选通过进行集成电路层20的动作测试,预先检查器件层22的半导体元件组无异常。

继而,将集成电路层10与集成电路层20相互接合(接合步骤S12)。即,经由粘结层7a以使半导体基板11的表面11a与半导体基板21的表面21a相互相对的方式,将集成电路层10与集成电路层20贴合。同时,通过将集成电路层10的多个连接用端子14的各个与集成电路层20的多个连接用端子24的各个接合,而将它们电连接。再者,在该接合阶段中,集成电路层10、20可为自晶圆分割的单一芯片,也可为包含多个芯片的集合体,或也可为分割前的晶圆状态。

继而,对检查用整流元件部15、25施加偏压(第1检查用电压施加步骤S13)。即,使探针接触于连接用端子26b及26c,在集成电路层10的正电源配线13a与集成电路层20的接地配线23b之间,施加使接地配线23b侧成为正电位的检查用的偏压。由此,正向的偏压被施加于检查用整流元件部15的整流元件15a及检查用整流元件部25的整流元件25b。因此,正向电流流至整流元件15a及25b,若连接用端子14与连接用端子24的连接正常,则整流元件15a及25b(或与整流元件15a及25b串联连接的另一发光元件)发光。

继而,根据在集成电路层20的背面21b侧所观察的检查用整流元件部25的发光、及在集成电路层10的背面11b侧所观察的检查用整流元件部15的发光中的至少一者,检查集成电路层10的多个连接用端子14与集成电路层20的多个连接用端子24的连接状态(第1检查步骤S 14)。具体而言,自集成电路层20的背面21b侧或自集成电路层10的背面11b侧对半导体集成电路装置1A进行拍摄。然后,将拍摄数据中所包含的亮点(检查用整流元件部15或25的发光)与预先准备的与检查用整流元件部15或25的发光位置相关的数据进行比较。通过该比较,在应发光的位置上若检查用整流元件部15或25未发光的情况或未达到规定的发光量的情况下,判定与该检查用整流元件部15或25对应的连接用端子14及24连接不良。

继而,对检查用整流元件部15、25施加偏压(第2检查用电压施加步骤S15)。即,使探针接触于连接用端子26a及26d,在集成电路层10的接地配线13b与集成电路层20的正电源配线23a之间,施加接地配线13b侧成为正电位的检查用的偏压。由此,正向的偏压被施加于检查用整流元件部15的整流元件15b及检查用整流元件部25的整流元件25a中。因此,正向电流流至整流元件15b及25a,若连接用端子14与连接用端子24的连接正常则整流元件15b及25a(或与整流元件15b及25a串联连接的另一发光元件)发光。

继而,根据在集成电路层20的背面21b侧所观察的检查用整流元件部25的发光、及在集成电路层10的背面11b侧所观察的检查用整流元件部15的发光中的至少一者,检查集成电路层10的多个连接用端子14与集成电路层20的多个连接用端子24的连接状态(第2检查步骤S16)。具体而言,自集成电路层20的背面21b侧或自集成电路层10的背面11b侧对半导体集成电路装置1A进行拍摄。而且,对比拍摄数据中所包含的亮点(检查用整流元件部15或25的发光)与预先所准备的与检查用整流元件部15或25的发光位置相关的基准数据上的亮点。通过该对比,在应发光的位置上检查用整流元件部15或25未发光的情况或未达到规定的发光量的情况下,判定与该检查用整流元件部15或25对应的连接用端子14及24连接不良。

对比拍摄数据与基准数据时,必需使它们的位置对准。因此,依次或同时获取来自检查用整流元件部15或25的发光影像、与集成电路层10或20所包含的集成电路的背面图案影像,在集成电路层10或20的布局数据与背面图案影像之间进行位置对准即可。再者,也可通过仅获取来自检查用整流元件部15或25的发光影像,对比该发光位置及与发光位置的特征性的配置相关的数据而进行位置对准。

在本实施方式的检查方法中,也可仅进行上述的步骤S13及S14、与步骤S15及S16的组合中的任一组合。换而言之,检查用整流元件部15及25也可分别仅具有整流元件15a及25b,或也可分别仅具有整流元件15b及25a。另外,也可通过将步骤S13中所获得的拍摄数据与步骤S14中所获得的拍摄数据进行比较(或重叠),对比上述比较数据(或重叠数据)与基准数据,而检查连接不良的有无。在例如整流元件15a及15b的位置相互接近的情况下等,通过使来自整流元件15a的光与来自整流元件15b的光对准而进行观察,可提高拍摄数据的可靠度。

与现有技术的课题一起叙述与由以上所说明的本实施方式的半导体集成电路装置1A的检查方法及通过半导体集成电路装置1A而获得的效果。

近年来,为了进一步提高电路的集成密度,正在开发在厚度方向上层叠多个形成有集成电路的基板或层而成的半导体集成电路装置。该半导体集成电路装置在各集成电路层之间包含凸块电极等电(层间)连接用端子。因各集成电路层的集成电路规模越大则连接用端子的数量越多,因而对连接用端子的导通检查必不可少。另外,优选与半导体集成电路装置的制造并行地对连接不良的原因进行分析,并将其反馈于制造技术中。

然而,半导体集成电路装置完成之后,层间连接用端子藏于层叠构造的内部,从而不易特定连接不良的产生部位。因此,若可以每层叠一层集成电路层便进行层间连接用端子的导通检查,则可特定连接不良的产生部位。进而,可有效地防止在具有连接不良部位的集成电路层上层叠新的集成电路层的徒劳。

在上述的本实施方式的半导体集成电路装置1A的检查方法中,通过例如凸块等将集成电路层10的多个连接用端子14与上述集成电路层20的多个连接用端子24相互电连接之后,经由集成电路层10的正电源配线13a(或接地配线13b)与集成电路层20的接地配线23b(或正电源配线23a),对检查用整流元件部15、25施加偏压。此时,在集成电路层10的连接用端子14与集成电路层20的连接用端子24良好地连接的情况下,会构成集成电路层10的正电源配线13a(或接地配线13b)~检查用整流元件部15~集成电路层10的连接用端子14~集成电路层20的连接用端子24~检查用整流元件部25~集成电路层20的接地配线23b(或正电源配线23a)的电流路径。

因此,流过该电流路径的电流的大小与将正电源配线13a(或接地配线13b)及接地配线23b(或正电源配线23a)所具有的电阻值、连接用端子14及24的电阻值、以及检查用整流元件部15及25的电阻值合计而得的电阻值成反比例。多数情况下,电源配线及接地配线的电阻值明显小于层间连接用端子的电阻值,另外,检查用整流元件部(整流元件)的电阻值为已知。因此,检查用整流元件部15、25的发光量主要依赖于连接用端子14、24的电阻值,若连接用端子14、24为互不连接的状态(即电阻值无限大),则检查用整流元件部15、25不发光。因此,通过观察检查用整流元件部15、25的发光的有无而检测连接用端子14、24的连接不良,再者通过观察发光量,可推断连接用端子14与连接用端子24之间的电阻值。

即,根据上述的半导体集成电路装置1A的检查方法及半导体集成电路装置1A,根据检查用整流元件部15、25中的至少一者的发光,可检查集成电路层10的多个连接用端子14与集成电路层20的多个连接用端子24的连接状态。因此,通过总括观察与多个连接用端子14、24的各个对应的发光的有无,可容易地判断连接不良的有无,因此与如现有那样通过探测逐次地检查多个端子的方法相比,可以每层叠一层集成电路层便在短时间内检查连接不良的有无。

另外,在层叠3层以上的集成电路层的情况下,若每层叠一层集成电路层便进行利用探测的检查,则焊垫的损伤或凹凸、污垢等会在之后的层叠步骤中成为不良的原因。根据本实施方式,可明显减少每次层叠的探测次数,或完全不进行探测,因此可减少连接不良。

另外,根据本实施方式,每层叠一层集成电路层便检查连接不良的有无可容易地进行,因此可防止在产生连接不良的集成电路层上层叠正常的集成电路层的徒劳。另外,可连续且简便地检测连接不良的部位,因此可加快用于集成电路层的改良的反馈,从而提高成品率。

另外,优选如本实施方式那样,用于对检查用整流元件部15施加检查用的偏压的配线是用于将电源电压供给至器件层12的半导体元件组的正电源配线13a,并且,用于对检查用整流元件部25施加检查用的偏压的配线是用于将电源电压供给至器件层22的半导体元件组的接地配线23b。而且,优选,相对于正电源配线13a反方向地连接检查用整流元件部15的整流元件15a,相对于接地配线23b反方向地连接检查用整流元件部25的整流元件25b。

或者,优选,用于对检查用整流元件部15施加检查用的偏压的配线是用于将电源电压供给至器件层12的半导体元件组的接地配线13b,并且,用于对检查用整流元件部25施加检查用的偏压的配线是用于将电源电压供给至器件层22的半导体元件组的正电源配线23a。而且,优选,相对于接地配线13b反方向地连接检查用整流元件部15的整流元件15b,相对于正电源配线23a反方向地连接检查用整流元件部25的整流元件25a。

在半导体集成电路装置1A具有上述构成的情况下,因在集成电路层10中,相对于正电源配线13a及接地配线13b分别反方向地连接检查用整流元件部15的整流元件15a及15b,因而在通常的动作时电流未流至检查用整流元件部15。同样地,因在集成电路层20中,相对于正电源配线23a及接地配线23b分别反方向地连接检查用整流元件部25的整流元件25a、25b,因而在通常的动作时电流也未流至检查用整流元件部25。然后,在检查时,经由正电源配线13a及接地配线23b或者经由接地配线13b及正电源配线23a对检查用整流元件部15、25施加成为正向(即,与通常的动作时的电源电压正负相反)的检查用偏压,由此可将电流供给至检查用整流元件部15、25而使其发光。因此,通过半导体集成电路装置1A具有上述构成,可利用既存的电源配线及接地配线检查层间连接不良的有无。

再者,关于检查用整流元件部15及25,在图2中表示了包含与整流元件串联连接的发光元件的构成的例子,但发光元件也可为除发光用二极管以外的元件。例如,图4是表示检查用整流元件部35B的构成的图。该检查用整流元件部35B可与图1所示的检查用整流元件部15及25进行替换。如图4所示,检查用整流元件部35B包含整流元件35a与相对于该整流元件35a串联连接的作为发光元件的发光用晶体管35e。另外,检查用整流元件部35B包含整流元件35b与相对于该整流元件35b串联连接的作为发光元件的发光用晶体管35f。

图5是表示检查用整流元件部35C的构成的图。该检查用整流元件部35C可与图1所示的检查用整流元件部15及25进行替换。如图5所示,检查用整流元件部35C包含整流元件35a与相对于该整流元件35a串联连接且正向连接于连接用端子14或24与正电源配线13a或23a之间的作为发光元件的低耐压二极管35g。另外,检查用整流元件部35C包含整流元件35b与相对于该整流元件35b串联连接且正向连接于连接用端子14或24与接地配线13b或23b之间的作为发光元件的低耐压二极管35h。

图6是表示检查用整流元件部35D的构成的图。该检查用整流元件部35D可与图1所示的检查用整流元件部15及25进行替换。如图6所示,检查用整流元件部35D包含整流元件35a与相对于该整流元件35a串联连接的作为发光元件的隧道电流电容器35i。另外,检查用整流元件部35D包含整流元件35b与相对于该整流元件35b串联连接的作为发光元件的隧道电流电容器35j。

为了减少由检查用的整流元件的追加引起的附加容量,优选在连接用端子或贯通配线的很近处配置整流元件,但连接用端子或贯通配线会妨碍发光检测。因此,如图2及图4~图6所示,通过将发光元件与整流元件分开设置,可离开贯通配线或连接用端子而配置该发光元件,从而容易观察发光。再者,作为发光元件,可应用根据电流而发光的所有半导体元件。另外,也可使各发光元件的发光波长互不相同。

作为整流元件15a及15b、25a及25b、以及35a及35b,优选为以下列举的各元件。即,此处所谓的整流元件是指对偏压进行非线性应答而使电流流动的具有接合构造的元件(二极管、晶体管、闸流晶体管等)。作为如此的接合构造,可列举:作为P型半导体与N型半导体的接合的PN结、P型半导体与不含杂质的I(本质(intrinsic))型半导体的接合、I型半导体与N型半导体的接合、在P型半导体与N型半导体之间插入I型半导体的PIN接合、作为半导体与金属的接合的肖特基接合、及在边界部分插入隧道电流流动的较薄的绝缘膜或空隙、点接触部分的隧道接合。其中,最优选为PN结。再者,PN结及PIN接合中的顺向偏压时的发光主要为复合发光,PN结及PIN接合中的反向偏压时的发光以及来自MOS晶体管的通道的发光主要为热载子发光。在隧道接合中,会产生热载子发光及复合发光两者。作为本实施方式中的整流元件,优选为也兼有发光功能的PN二极管。

再者,对于隧道接合元件,存在上述正向电流的大小与反方向电流的大小大致相等的情况。然而,隧道接合有在低偏压时电流不流动,在高偏压时使较大的电流流动的特性。因此,在检查时能够使得在施加有较高的偏压时电流流动,在通常的使用条件下电流不流动。另外,在隧道接合部分产生基于所提供的电压差的热载子发光,且若构成隧道接合部分的一方的半导体为P型而另一方的半导体为N型则也产生复合发光。因此,可用作兼有发光功能的整流元件,或者也可用作发光元件。

另外,在本实施方式的半导体集成电路装置1A的检查方法中,集成电路层10的检查用整流元件部15与集成电路层20的检查用整流元件部25同时发光,在这些检查用整流元件部15与检查用整流元件部25之间存在各集成电路层10、20的配线层13、23。另外,在集成电路层10与集成电路层20之间,也存在作为连接用端子14、24的凸块等。因此,来自检查用整流元件部15、25的光由配线层13、23或连接用端子14、24所遮蔽,因此在自各个侧观察来自检查用整流元件部15(或25)的光时,来自检查用整流元件部25(或15)的光不易妨碍观察。再者,也可致力于研究配线层13、23的配线密度分布或配线形状以有效地遮蔽这些的光。另外,也可对粘结层7a的材料或成分进行选择以有效地遮蔽这些的光。

(第2实施方式)

图7是表示作为第2实施方式的半导体集成电路装置1B的构成的剖面图。本实施方式的半导体集成电路装置1B包含集成电路层20及30。再者,在本实施方式中,以集成电路层30所具有的半导体基板11的背面11b与集成电路层20所具有的半导体基板21的表面21a相互相对的方式,将集成电路层30、20相互接合。在集成电路层30中,除以下叙述的构成以外的其它构成与上述实施方式的集成电路层10相同。

集成电路层30包含具有表面11a及背面11b的半导体基板(支撑层)11、设置于半导体基板11的表面11a的器件层12、设置于器件层12上的配线层13、及用于电连接于集成电路层20的多个连接用端子(电极)34。配线层13的多个配线中也包含用于对多个半导体元件施加电源电压的正电源配线13a及接地配线13b。

多个连接用端子34设置于半导体基板11的背面11b上。集成电路层30的多个连接用端子34各个与集成电路层20的多个连接用端子24各个配置于背面11b上及表面21a上相互相对的位置上,且通过相互接触而电连接。多个连接用端子34通过例如凸块电极而良好地构成。

另外,集成电路层30包含与信号配线用的多个连接用端子34各个一对一地对应的多个第1检查用整流元件部15。检查用整流元件部15的构成与第1实施方式相同。其中,整流元件15a反方向连接于集成电路层10的正电源配线13a与连接用端子34之间,整流元件15b反方向连接于集成电路层10的接地配线13b与连接用端子34之间。整流元件15a及15b与连接用端子34经由贯通配线37而连接。贯通配线37是用于将配线层13的配线与背面11b上的多个连接用端子34相互连接的TSV。

半导体集成电路装置1B进而包含处置基板8。处置基板8经由粘结层7b而接合于集成电路层30的表面11a侧。

在本实施方式的半导体集成电路装置1B中,通过图3所示的检查方法,可良好地检查连接用端子34与连接用端子14的连接状态。其中,来自集成电路层30的检查用整流元件部15的光由配线层13及处置基板8所遮蔽,因此自背面21b侧观察来自集成电路层20的检查用整流元件部25的光即可。由此,可获得与上述第1实施方式相同的作用及效果。

(第3实施方式)

图8是表示作为第3实施方式的半导体集成电路装置1C的构成的剖面图。本实施方式的半导体集成电路装置1C在厚度方向上层叠集成电路层10、20及40而成。再者,在本实施方式中,集成电路层10及20的各构成及连接构造与第1实施方式相同,以集成电路层20所具有的半导体基板21的背面21b与集成电路层40所具有的半导体基板41的表面41a相互相对的方式,将集成电路层20、40相互接合。

集成电路层40包含具有表面41a及背面41b的半导体基板(支撑层)41、设置于半导体基板41的表面41a的器件层42、设置于器件层42上的配线层43、及用于电连接于集成电路层20的多个连接用端子(电极)44。器件层42含有由多个半导体元件构成的半导体元件组。

配线层43包含用于将器件层42中所包含的多个半导体元件相互电连接的多个配线。这些多个配线中包含用于对多个半导体元件施加电源电压的正电源配线43a及接地配线43b。在本实施方式中,集成电路层40的正电源配线43a及接地配线43b与集成电路层10、20的正电源配线13a、23a及接地配线13b、23b相互独立地配置,未形成相互的连接。

多个连接用端子44设置于配线层43上。集成电路层20的多个连接用端子26各个与多个连接用端子44各个配置于背面21b上及表面41a上相互相对的位置上,且通过相互接触而电连接。多个连接用端子44的各个通过例如凸块电极而良好地构成。

另外,集成电路层40进而包含多个检查用整流元件部45。多个检查用整流元件部45各个形成于器件层42,与信号配线用的多个连接用端子44各个一对一地对应。多个检查用整流元件部45分别包含整流元件45a及45b。整流元件45a反方向连接于集成电路层40的正电源配线43a与连接用端子44之间,整流元件45b反方向连接于集成电路层40的接地配线43b与连接用端子44之间。再者,检查用整流元件部45的详细的构成例及变形例与第1实施方式的检查用整流元件部15、25相同。

集成电路层40为了将半导体基板41的表面41a上的配线层43的配线与背面41b上的多个连接用端子(电极)46相互连接,进而包含多个贯通配线(TSV)47。多个连接用端子46包含连接用端子46a~46f。连接用端子46a及46b分别经由贯通配线47而与正电源配线43a及接地配线43b电连接。连接用端子46c经由贯通配线47、连接用端子44、连接用端子26a及贯通配线27而与集成电路层20的正电源配线23a电连接。连接用端子46d经由贯通配线47、连接用端子44、连接用端子26b及贯通配线27而与集成电路层20的接地配线23b电连接。连接用端子46e经由贯通配线47、连接用端子44、连接用端子26c、贯通配线27、连接用端子24及14而与集成电路层10的正电源配线13a电连接。连接用端子46f经由贯通配线47、连接用端子44、连接用端子26d、贯通配线27、连接用端子24及14而与集成电路层10的接地配线13b电连接。如此,为了相互独立地配设集成电路层10、20及40的各电源系统,而设置有连接用端子46a~46f。连接用端子46a~46f及连接于它们的贯通配线或连接用端子构成用于对检查用整流元件部15、25及45施加偏压的电压施加部。

半导体集成电路装置1C进而包含粘结层6。粘结层6设置于集成电路层20与集成电路层40的间隙中,将集成电路层20及集成电路层40机械地接合。再者,该粘结层6优选为含有可遮蔽来自检查用整流元件部25的光的材料。

在本实施方式的半导体集成电路装置1C中,在图3所示的检查方法中,通过分别将集成电路层10替换成集成电路层20,将集成电路层20替换成集成电路层40,可良好地检查连接用端子44与连接用端子26的连接状态。其中,来自集成电路层20的检查用整流元件部25的光由配线层43所遮蔽,因此自背面41b侧观察来自集成电路层40的检查用整流元件部45的光即可。由此,可获得与上述第1实施方式相同的作用及效果。

(第4实施方式)

图9是表示作为第4实施方式的半导体集成电路装置1D的构成的剖面图。本实施方式的半导体集成电路装置1D在厚度方向上层叠集成电路层10、50及40而成。再者,在本实施方式中,集成电路层10的构成与第1实施方式相同,集成电路层40的构成与第3实施方式相同。在本实施方式中,以集成电路层10的半导体基板11的表面11a与集成电路层50的半导体基板51的背面51b相互相对,且半导体基板51的表面51a与集成电路层40的半导体基板41的表面41a相互相对的方式,将集成电路层10、50及40相互接合。

集成电路层50包含具有表面51a及背面51b的半导体基板(支撑层)51、设置于半导体基板51的表面51a的器件层52、设置于器件层52上的配线层53及用于电连接于集成电路层40的多个连接用端子(电极)54。器件层52含有由多个半导体元件构成的半导体元件组。

配线层53包含用于将器件层52中所包含的多个半导体元件相互电连接的多个配线。这些多个配线中包含用于对多个半导体元件施加电源电压的正电源配线53a及接地配线53b。在本实施方式中,集成电路层10、40及50的各正电源配线13a、43a及53a以及各接地配线13b、43b及53b相互独立地配置,未形成相互的连接。

多个连接用端子54设置于配线层53上。多个连接用端子54各个与集成电路层40的多个连接用端子44各个配置于表面51a上及表面41a上相互相对的位置上,且通过相互接触而电连接。多个连接用端子54的各个通过例如凸块电极而良好地构成。

另外,集成电路层50进而包含多个检查用整流元件部55。多个检查用整流元件部55各个形成于器件层52,与信号配线用的多个连接用端子54各个一对一地对应。多个检查用整流元件部55分别包含整流元件55a及55b。整流元件55a反方向连接于集成电路层50的正电源配线53a与连接用端子54之间,整流元件55b反方向连接于集成电路层50的接地配线53b与连接用端子54之间。再者,检查用整流元件部55的详细的构成例及变形例与第1实施方式的检查用整流元件部15、25相同。

集成电路层50为了将半导体基板51的表面51a上的配线层53的配线与背面51b上的多个连接用端子(电极)56相互连接,进而包含多个贯通配线(TSV)57。集成电路层40的连接用端子46c及46d的各个经由贯通配线47、连接用端子44、连接用端子54而与集成电路层50的正电源配线53a及接地配线53b的各个电连接。另外,集成电路层40的连接用端子46e及46f的各个经由贯通配线47、连接用端子44、连接用端子54、贯通配线57、连接用端子56、连接用端子14而与集成电路层10的正电源配线13a及接地配线13b的各个电连接。如此,为了相互独立地配设集成电路层10、50及40的各电源系统,而设置有连接用端子46a~46f。连接用端子46a~46f及连接于它们的贯通配线或连接用端子构成用于对检查用整流元件部15、55及45施加偏压的电压施加部。

在本实施方式的半导体集成电路装置1D中,在图3所示的检查方法中,通过分别将集成电路层10替换成集成电路层50,将集成电路层20替换成集成电路层40,可良好地检查连接用端子54与连接用端子44的连接状态。其中,来自集成电路层50的检查用整流元件部55的光由配线层43及53所遮蔽,因此自背面41b侧观察来自集成电路层40的检查用整流元件部45的光即可。由此,可获得与上述第1实施方式相同的作用及效果。

(第5实施方式)

图10是表示作为第5实施方式的半导体集成电路装置1E的构成的剖面图。本实施方式的半导体集成电路装置1E在厚度方向上层叠集成电路层10A、20A、10B及20B而成。在本实施方式中,集成电路层10A及20A各自的构成及相互的接合构造与第1实施方式的集成电路层10及20相同。另外,集成电路层10B及20B各自的构成及相互的接合构造除下述的方面以外与第1实施方式的集成电路层10及20相同。

即,集成电路层10B以上述半导体基板11的背面11b与集成电路层20A的半导体基板21的背面21b相对的方式,经由粘结层7c而与集成电路层20A接合。

另外,集成电路层10B为了将半导体基板11的表面11a上的配线层13的配线与背面11b上的多个连接用端子(电极)16相互连接,而包含多个贯通配线(TSV)17。多个连接用端子16与集成电路层20A的信号配线用的多个连接用端子26一对一地对应而配置,集成电路层10B的多个连接用端子16与集成电路层20A的多个连接用端子26相互电连接。

集成电路层20B的多个连接用端子26包含端子电极26a~26f。连接用端子26a及26b的各个经由贯通配线27与集成电路层20B的正电源配线23a及接地配线23b的各个电连接。连接用端子26c经由集成电路层20B的贯通配线27及连接用端子24、集成电路层10B的连接用端子14、贯通配线17及连接用端子16以及集成电路层20A的连接用端子26及贯通配线27,而与集成电路层20A的正电源配线23a电连接。连接用端子26d也通过相同的构成,而与集成电路层20A的接地配线23b电连接。另外,连接用端子26e经由集成电路层20B的贯通配线27及连接用端子24、集成电路层10B的连接用端子14、贯通配线17及连接用端子16、集成电路层20A的连接用端子26、贯通配线27及连接用端子24以及集成电路层10A的连接用端子14,而与集成电路层10A的正电源配线13a电连接。连接用端子26f也通过相同的构成,而与集成电路层10A的接地配线13b电连接。

如此,在本实施方式中,为了相互独立地配设集成电路层10A、20A及20B的各电源系统,而在集成电路层20B设置有连接用端子26a~26f。连接用端子26a~26f及连接于它们的贯通配线或连接用端子构成用于对检查用整流元件部15及25施加偏压的电压施加部。

在本实施方式的半导体集成电路装置1E中,在图3所示的检查方法中,通过分别将集成电路层10替换成集成电路层20A,将集成电路层20替换成集成电路层20B,可良好地检查自集成电路层20B的连接用端子24至集成电路层20A的连接用端子26的信号路径的连接状态。其中,来自集成电路层20A的检查用整流元件部25的光由集成电路层10B的配线层13及集成电路层20B的配线层23所遮蔽,因此自集成电路层20B的背面21b侧观察来自集成电路层20B的检查用整流元件部25的光即可。由此,可获得与上述第1实施方式相同的作用及效果。

尤其,在层叠3层以上集成电路层,且共同设置于集成电路层间的总线(bus)配线的基板间配线遍及3层以上而连续的情况下,如本实施方式那样通过在最上部的集成电路层20B与第3层以后的集成电路层20A之间施加检查用的偏压,可进行遍及3层以上的集成电路层20A、10B及20B的连接不良的检测或电阻值的推测。在本实施方式中,利用接合集成电路层10A及20A而成的层叠物与接合集成电路层10B及20B而成的层叠物个别地进行检查之后,在一个层叠物上层叠其它层叠物,在连接用端子26a及26d之间或连接用端子26b及26c之间施加检查用的偏压,由此可总括检测最上层(集成电路层20B)与第2层(集成电路层10B)的层间连接、第2层(集成电路层10B)与第3层(集成电路层20A)的层间连接、以及第2层内及第3层内的TSV的连接不良。

再者,本实施方式的半导体集成电路装置1E具备接合有第1实施方式所涉及的2个半导体集成电路装置1A的构成,如此接合的2个半导体集成电路装置可具备上述的第1实施方式至第4实施方式的任一构成,另外也可组合互不相同的构成。

(第6实施方式)

图11是表示作为第6实施方式的半导体集成电路装置1F的构成的剖面图。本实施方式的半导体集成电路装置1F在厚度方向上层叠集成电路层10C及20C而成。在本实施方式中,集成电路层10C及20C各自的构成及相互的接合构造除下述的方面以外与第1实施方式的集成电路层10及20各自的构成相同。

本实施方式的集成电路层10C及20C分别包含连接用端子14A及24A而代替第1实施方式的连接用端子14及24。连接用端子14A并非如第1实施方式那样的凸块电极,而是焊垫状的电极。另外,作为连接用端子24A,TSV28a的一端自集成电路层20C的表面21a突出,该一端与连接用端子14A相接。TSV28a的另一端在信号配线的情况下与设置于半导体基板21的背面21b上的再配线29相接,经由与该再配线29相接的其它TSV28b而连接于配线层23的配线。另外,TSV28a的另一端在电源配线或接地配线的情况下与设置于半导体基板21的背面21b上的连接用端子26相接。

如本实施方式那样的层间连接构造通过如下的方式而制成:例如表面11a及21a为相互相对的方向而将集成电路层10C与集成电路层20C接合之后,通过蚀刻等形成自半导体基板21的背面21b到达集成电路层10C的连接用端子14A的第1孔、及自背面21b到达配线层23的第2孔,在第1及第2孔中埋入金属材料之后,在其上形成再配线29。或者,通过将集成电路层10C与集成电路层20C接合之后,形成自背面21b到达连接用端子14A的孔,在该孔中埋入金属材料之后,在其上形成连接用端子26而制成。关于第1实施方式中所说明的作用及效果,即使在如本实施方式那样的层间连接构造中也可良好地获得。

(第7实施方式)

图12是表示作为第7实施方式的半导体集成电路装置1G的构成的剖面图。本实施方式的半导体集成电路装置1G在厚度方向上层叠集成电路层20D及30D而成。在本实施方式中,集成电路层20D及30D各自的构成及相互的接合构造除下述的方面以外与第1变形例的集成电路层20及30各自的构成相同。

本实施方式的集成电路层20D及30D自具有所谓的SOI(Silicon On Insulator,绝缘体上硅)构造的基板除去硅层而制成,分别包含氧化膜层21D及11D作为支撑层。集成电路层20D的多个贯通配线27贯通氧化膜层21D而形成,其背面21b侧的一端作为多个连接用端子26A而自氧化膜层21D露出。同样地,集成电路层30D的多个贯通配线37贯通氧化膜层11D而形成,其背面31b侧的一端作为多个连接用端子34A而自氧化膜层11D露出。多个连接用端子34A的各个与集成电路层20D的多个连接用端子24的各个电连接。再者,多个贯通配线27及37并非成为如上述各实施方式那样的TSV,而仅成为接触孔。

如本实施方式那样,即使在集成电路层20D及30D包含氧化膜层21D及11D作为支撑层的情况下,也可良好地获得第1实施方式中所说明的作用及效果。

再者,在上述的第1实施方式至第7实施方式中,作为连接用端子的凸块电极可为单侧凸块,也可代替凸块电极而使用TSV。另外,也可不设置凸块电极,而直接将作为连接用端子的金属膜彼此接合。另外,在上述各实施方式中为了集成电路层彼此的接合而使用粘结层,但也可分别在各集成电路层的连接用端子以外的区域形成金属膜,直接将该金属膜彼此接合。另外,若各集成电路层的机械强度充分,则也可在2个集成电路层之间留出空隙。

(第8实施方式)

图13是表示作为第8实施方式的电源配线及接地配线的构成的图。如图13所示,在本实施方式中,为了对多个检查用整流元件部65施加偏压,针对一个集成电路层60设置有至少双系统(本实施方式中为双系统)的电源配线63a及63b。另外,集成电路层60的多个连接用端子64沿着相互正交的两个方向二维状地排列。再者,在图13中,一并表示有另一个集成电路层的检查用整流元件部66及接地配线67。

一个电源配线63a对与多个连接用端子64中呈格纹状配置的一部分连接用端子64电连接的检查用整流元件部65施加偏压。另外,另一电源配线63b对与多个连接用端子64中其余的连接用端子64电连接的检查用整流元件部65施加偏压。因此,连接于自电源配线63a施加有偏压的检查用整流元件部65的连接用端子64、与连接于自电源配线63b施加有偏压的检查用整流元件部65的连接用端子64在上述两个方向上未邻接。

通过如本实施方式那样构成电源配线,可分开观察来自连接于上述一部分连接用端子64的检查用整流元件部65的发光、与来自连接于其余的连接用端子64的检查用整流元件部65的发光。若不存在邻接的连接用端子64彼此的短路,则各检查用整流元件部65仅在自对应的电源配线63a或63b施加有偏压时发光,在邻接的连接用端子64彼此发生短路的情况下,即使对电源配线63a及63b的任一个施加偏压,该检查用整流元件部65也发光。可通过观察该发光,而检测邻接的连接用端子64彼此短路。

再者,对至少设置双系统电源配线的例子进行了说明,但通过至少设置双系统接地配线,或组合各双系统以上的电源配线及接地配线,可发挥与上述相同的效果。

(第9实施方式)

图14是表示作为第9实施方式的电压施加部68的构成的图。电压施加部68连接于图1所示的集成电路层20的正电源配线23a与集成电路层10的接地配线13b之间(或正电源配线13a与接地配线23b之间)。该电压施加部68包含一个以上的光电转换元件(二极管)68a。在图14所示的例子中,串联连接有2个光电转换元件68a。光电转换元件68a的阳极侧与正电源配线23a(或正电源配线13a)连接,光电转换元件68a的阴极侧与接地配线13b(或接地配线23b)连接。光电转换元件68a通过来自半导体集成电路装置1A的外部的能量输入(光输入),产生检查用的偏压。

通过将如本实施方式那样的电压施加部68设置于集成电路层10及20中的至少一层中,可不利用探测而进行对检查用整流元件部15、25的偏压的施加,因此可进一步减少检查时的探测次数(或不进行探测)。再者,实现如此的电压施加部的元件并不限定于光电转换元件,若为通过来自外部的能量线的入射可产生电动势的元件,则也可应用其它种类的元件。例如,也可将作为电动势元件的线圈部设置于集成电路层10及20中的至少一层中。在此情况下,可通过对线圈部照射磁场而产生偏压。

(第10实施方式)

图15是表示作为第10实施方式的检查装置100A的构成的图。该检查装置100A用于良好地实施上述的第1实施方式至第9实施方式的半导体集成电路装置(图中以第1实施方式所涉及的半导体集成电路装置1A为代表而表示)的检查方法的装置。

检查装置100A为了将来自半导体集成电路装置1A的检查用整流元件部15或25的发光拍摄为图像,而包括对包含该发光的影像进行拍摄的相机101、产生检查用的足够大的偏压的电源102、用于对检查用整流元件部15或25向地施加该偏压的探针(电压施加机构)103a及103b、及根据来自相机101的图像检查连接不良的有无的控制系统104。在相机101与半导体集成电路装置1A之间设置有物镜109及成像透镜110,相机101经由物镜109及成像透镜110对来自检查用整流元件部15或25的发光进行拍摄。相机101经由相机缆线101a而与控制系统104电连接,通过控制系统104控制上述动作,并且将拍摄数据向控制系统104传送。

另外,检查装置100A进而包含用于观察集成电路的图案的照明系统105。照明系统105包含光导106、灯光源107及光束分光器108。自灯光源107所射出的光通过光导106到达光束分光器108。光束分光器108配置于物镜109与成像透镜110之间,朝向半导体集成电路装置1A对来自灯光源107的光进行反射,并且使从半导体集成电路装置1A出来的光透过。通过该照明系统105,相机101除可对来自检查用整流元件部15或25的发光进行拍摄以外,也可对最上层的集成电路层20的集成电路图案进行拍摄。包含该集成电路图案的图像在对比拍摄数据与基准数据时,在布局数据与背面图案影像之间进行位置对准时而使用。

再者,上述的检查装置100A的构成要素中,除控制系统104及灯光源107以外的构成要素优选为容纳于暗箱120的内部。本实施方式中相机101配置于半导体集成电路装置1A的上方,但相机101也可配置于半导体集成电路装置1A的下方。

(第11实施方式)

图16是表示作为第11实施方式的检查装置100B的构成的图。该检查装置100B用于良好地实施上述的第1实施方式至第9实施方式的半导体集成电路装置的检查方法的装置。

该检查装置100B除包含上述的检查装置100A(图15)的构成以外,也包含激光光源112、激光扫描仪113及波长选择镜114。这些的构成要素用于对具有例如图14所示的构成的电压施加部照射作为能量线的激光的要素。激光光源112生成电压施加部的电动势产生所优选的波长的激光。该激光光源112通过激光控制电缆112a而与控制系统104电连接,其射出时序等由控制系统104所控制。激光扫描仪113自激光光源112经由光纤缆线113a接收激光,变更向半导体集成电路装置1A的激光的照射位置。激光扫描仪113通过扫描仪控制电缆113b而与激光光源112电连接,控制其扫描方向。

波长选择镜114配置于光束分光器108与成像透镜110之间。波长选择镜114朝向半导体集成电路装置1A对自激光扫描仪113所射出的激光进行反射。另外,波长选择镜114使来自半导体集成电路装置1A的光学影像朝向相机101而通过。

如本实施方式那样,用于检查半导体集成电路装置的检查装置也可具备照射用于半导体集成电路装置的电动势产生的能量线的构成而代替图15所示的探针103a及103b以及偏压电源102。再者,为了防止激光的反射光射入相机101,在波长选择镜114与相机101之间设置凹口波滤波器115即可。或者,为了也使用激光作为激光显微镜,也可另外设置检测激光的反射光的传感器。另外,在本实施方式中,自半导体集成电路装置1A的上方(与相机101相同的侧)照射激光,但也可设为自半导体集成电路装置1A的下方(与相机101相反的侧)照射激光的构成。另外,为了特定激光的照射

半导体集成电路装置的检查方法及半导体集成电路装置专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0