专利摘要

本发明公开了一种基于可编程基本逻辑单元的数据移位电路,其包括2n位移位寄存器、n输入查找表和配置信息存储块;所述2n位移位寄存器包括串联的2n个移位寄存器单元,输入数据在该串联的2n个移位寄存器单元中逐位移动;所述n输入查找表被配置成多路选择开关,其根据从配置信息存储模块输入的移位位数m选择输出第m个移位寄存器单元的输出数据;所述配置信息存储模块,用于存储输入数据的移位位数m,其输出与n输入查找表的输出相连。该数据移位电路是在BLE结构上基于复用BLE内部的可配置CSRAM实现,同时只需要一个时钟信号即可以完成移位寄存器功能。

权利要求

1.一种基于可编程基本逻辑单元的数据移位电路,其包括:多个串联的移位寄存器单元,所述移位寄存器单元由两级串联的带门控开关缓冲器的可编程基本逻辑单元中的静态存储器构成,其中所述移位寄存器单元的数据输入端为第一级静态存储器的门控开关缓冲器的输入端;所述移位寄存器单元的数据输出端为第二级静态存储器的输出,所述移位寄存器单元的时钟端与第一级静态存储器的门控开关缓冲器的门控开关输入端直接相连,并与第二级静态存储器的门控开关缓冲器的门控开关输入端通过一反相器相连。

2.如权利要求1所述的电路,其特征在于,所述数据移位电路还包括由可编程基本逻辑单元的LUT配置成的多路选择开关电路和配置信息存储电路;其中所述配置信息存储电路用于存储表示移位位数m的配置信息,所述多路选择开关电路根据所述移位配置信息选择输出第m个移位寄存器单元的输出数据。

3.如权利要求2所述的电路,其特征在于,所述构成移位寄存器单元的静态存储器包括两个传输门、两个反相器、两个控制端和两个双向端口,其第一个双向端口经第一个传输门后与第一个反相器的输入和第二个反相器的输出相连,第一个反相器的输出与第二个传输门相连,第二个双向端口经第二个传输门与第一个反向启动额输出和第二个反相器的输入相连,第二个反相器的输出与第一个传输门相连;两个控制端分别控制两个传输门是否导通,当两传输门均导通时,两双向端口为逻辑反向关系。

4.如权利要求3所述的电路,其特征在于,在所述可编程基本逻辑单元的数据移位寄存工作模式下,传输门M1、M2被配置为导通状态。

5.如权利要求3所述的电路,其特征在于,所述带门控开关缓冲器的静态存储器还包括带门控开关缓冲器,所述带门控开关缓冲器的输出端与所述静态存储器的第一双向端口相连,所述静态存储器的第二双向端口与下一级开门控开关缓冲器的输入相连。

6.一种基于可编程基本逻辑单元的数据移位电路,其包括:2n位移位寄存器、n输入查找表和配置信息存储块;

所述2n位移位寄存器包括串联的2n个移位寄存器单元,输入数据在该串联的2n个移位寄存器单元中逐位移动;

所述n输入查找表被配置成多路选择开关,其根据从配置信息存储模块输入的移位位数m选择输出第m个移位寄存器单元的输出数据;

所述配置信息存储模块,用于存储输入数据的移位位数m,其输出与n输入查找表的输出相连。

7.如权利要求6所述的数据移位电路,其特征在于,所述移位寄存器单元由两级串联的带门控开关缓冲器的可编程基本逻辑单元中的静态存储器构成,其中所述移位寄存器单元的数据输入端为第一级静态存储器的门控开关缓冲器的输入端;所述移位寄存器单元的数据输出端为第二级静态存储器的输出,所述移位寄存器单元的时钟端与第一级静态存储器的门控开关缓冲器的门控开关输入端直接相连,并与第二级静态存储器的门控开关缓冲器的门控开关输入端通过一反相器相连。

8.如权利要求7所述的数据移位电路,其特征在于,所述构成移位寄存器单元的静态存储器包括两个传输门、两个反相器、两个控制端和两个双向端口,其第一个双向端口经第一个传输门后与第一个反相器的输入和第二个反相器的输出相连,第一个反相器的输出与第二个传输门相连,第二个双向端口经第二个传输门与第一个反向启动额输出和第二个反相器的输入相连,第二个反相器的输出与第一个传输门相连;两个控制端分别控制两个传输门是否导通,当两传输门均导通时,两双向端口为逻辑反向关系。

9.如权利要求6所述的数据移位电路,其特征在于,所述配置信息存储模块由可编程基本逻辑单元中的静态存储器构成。

10.一种由基于可编程基本逻辑单元的数据移位寄存器实现的数据移位方法,其中所述数据移位寄存器包括2n位移位寄存器、n输入查找表和配置信息存储块;该方法包括:

步骤1:在可编程基本逻辑单元的常规模式下,将n输入查找表配置成多路选择开关;

步骤2:输入数据串行输入到所述2n位移位寄存器的数据输入端,所述2n位移位寄存器包括串联的2n个移位寄存器单元,所述输入数据在时钟脉冲的作用下在所述串联的2n个移位寄存器单元中逐位移动;

步骤3:所述多路选择开关根据从配置信息存储模块输入的移位信息,选择第m个所述移位寄存器单元的输出数据,将其作为移位后的数据进行输出,其中所述移位信息为移位位数m。

说明书

技术领域

本发明属于电子电路设计领域,具体涉及一种基于可编程基本逻辑单元的数据移位寄存电路。

背景技术

可编程基本逻辑单元BLE(Basic Logic Element)是FPGA中最小的逻辑单元,它包含一个n(n≥2)输入的查找表LUT(Lookup Table)、一个触发器以及进位链和级联链等。由若干个BLE和控制逻辑互连构成FPGA的基本单元LC(Logic Cluster)。每个BLE包括一个带n输入的查找表和一个触发器,查找表由可配置的静态存储器(CSRAM)构成的函数发生器组成,用来快速实现组合逻辑,触发器用来实现时序逻辑。BLE的输出可以通过触发器寄存输出,也可以旁路直接输出。

BLE作为FPGA内部核心单元模块,具备三种基本工作模式如下:

1、常规模式下,BLE内部带n个输入的查找表可实现任意n输入函数的逻辑功能,对于更多输入变量的逻辑功能,则须用多个BLE级联对其进行扩展;

2、运算模式下完成1位全加/全减器;

3、加/减计数模式或者可清零计数模式下完成一位计数。

对于最终BLE工作于哪种基本模式和如何输出,由内部配置CSRAM和外部控制信号决定。

随着集成电路设计复杂度的不断提高,要求BLE不仅需要实现上述基本工作模式外,还需要提供分布式数据存储和数据移位寄存操作功能。目前,国外XILINX、ALTERA等可编程逻辑器件供应商掌握大量的FPGA开发技术,其中文献[1](Xilinx Corporation,“Virtex II Pro and Virtex II Pro X Platform FPGAs:Complete Data Sheet”,2005)中XILINX公司提出了一种具有移位寄存器功能的BLE结构,此外专利申请CN200810038576.1也提出了一种同时具有分布式数据存储和数据移位寄存操作功能的LE结构,但上述结构均需要一个产生两相非交叠时钟信号的时序电路。

本发明提出具有移位寄存器功能的BLE结构,该结构基于复用BLE内部的可配置CSRAM,同时只需要一个时钟信号即可以完成移位寄存器功能。

发明内容

为解决上述问题,本发明提出了一种基于可编程基本逻辑单元的数据移位电路,其包括:多个串联的移位寄存器单元,所述移位寄存器单元由两级串联的带门控开关缓冲器的可编程基本逻辑单元中的静态存储器构成,其中所述移位寄存器单元的数据输入端为第一级静态存储器的门控开关缓冲器的输入端;所述移位寄存器单元的数据输出端为第二级静态存储器的输出,所述移位寄存器单元的时钟端与第一级静态存储器的门控开关缓冲器的门控开关输入端直接相连,并与第二级静态存储器的门控开关缓冲器的门控开关输入端通过一反相器相连。

本发明还提出了一种基于可编程基本逻辑单元的数据移位电路,其包括:2n位移位寄存器、n输入查找表和配置信息存储块;

所述2n位移位寄存器包括串联的2n个移位寄存器单元,输入数据在该串联的2n个移位寄存器单元中逐位移动;

所述n输入查找表被配置成多路选择开关,其根据从配置信息存储模块输入的移位位数m选择输出第m个移位寄存器单元的输出数据;

所述配置信息存储模块,用于存储输入数据的移位位数m,其输出与n输入查找表的输出相连。

本发明还提出了一种由基于可编程基本逻辑单元的数据移位寄存器实现的数据移位方法,其中所述数据移位寄存器包括2n位移位寄存器、n输入查找表和配置信息存储块;该方法包括:

步骤1:在可编程基本逻辑单元的常规模式下,将n输入查找表配置成多路选择开关;

步骤2:输入数据串行输入到所述2n位移位寄存器的数据输入端,所述2n位移位寄存器包括串联的2n个移位寄存器单元,所述输入数据在时钟脉冲的作用下在所述串联的2n个移位寄存器单元中逐位移动;

步骤3:所述多路选择开关根据从配置信息存储模块输入的移位信息,选择第m个所述移位寄存器单元的输出数据,将其作为移位后的数据进行输出,其中所述移位信息为移位位数m。

本发明提出具有移位寄存器功能的BLE结构,该结构基于复用BLE内部的可配置CSRAM,同时只需要一个时钟信号即可以完成移位寄存器功能。

附图说明

图1是可配置的静态存储器CSRAM的内部结构图;

图2是可配置的静态存储器CSRAM的外部逻辑示意图;

图3是本发明中带门控开关缓冲器的可配置的静态存储器CSRAM的逻辑示意图;

图4是本发明中移位寄存器单元的内部结构示意图;

图5是本发明中移位寄存器单元的外部逻辑示意图;

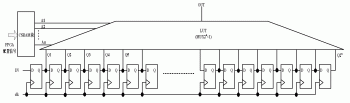

图6是本发明中基于可编程基本逻辑单元的移位寄存器的结构示意图。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

FPGA芯片的可重复配置特性来源于器件内部众多的静态存储器CSRAM,这些CSRAM单元的内容决定了芯片所要实现的具体逻辑功能以及用到的输入、输出端口等,相当于对芯片进行了配置。在实现一个具体的电路时,首先需要确定CSRAM的内容,然后,FPGA才会按照用户设定的模式工作。FPGA中的CSRAM有多个用途,第一个用途是存储FPGA的逻辑功能块的配置信息,这些配置信息设定了逻辑功能块的工作模式及其所要完成的具体任务。第二个用途是存储与FPGA中的布线资源相关的配置信息,这些配置信息用来确定各个逻辑功能块之间的信号传输路径。CSRAM的第三个用途是存储与IO相关的配置信息,这些配置信息将用来确定芯片与片外信号之间的通信等。

本发明公开了一种基于可编程基本逻辑单元BLE的数据移位寄存电路,其包括:2n位移位寄存器、n个输入LUT、配置信息存储CSRAM块等;其中,n个输入LUT在可编程基本逻辑单元BLE的移位寄存器模式下被配置为MUX2n×1的多路选择开关功能。

所述2n位移位寄存器由多个基于可编程基本逻辑单元BLE中的可配置的静态存储器CSRAM构成。其中,可编程基本逻辑单元BLE通常的CSRAM的结构如图1所示,该CSRAM包括两个传输门M1、M2、两个反相器INV1、INV2、两个控制端cs1、cs2和两个双向端口io1、io2,其第一个双向端口io1经第一个传输门M1后与第一个反相器INV1的输入和第二个反相器INV2的输出相连,第一个反相器INV1的输出与第二个传输门M2相连,第二个双向端口io2经第二个传输门M2与第一个反相器输出INV1和第二个反相器INV2的输入相连,第二个反相器INV2的输出与第一个传输门M1相连;两个控制端cs1、cs2分别控制传输门M1、M2是否导通或关闭,当M1和M2均导通时,io1和io2为逻辑反向关系。图2为该带四个端口的CSRAM的外部逻辑结构示意图,其中io1和io2均为双向端口,可配置为输入端或输出端;cs1和cs2分别为io1和io2的控制端。所述可编程基本逻辑单元电路BLE在基本的工作模式即常规模式、运算模式和加/减计数模式或数据移位寄存模式下工作,不同的工作模式均需要通过对大量的上述CSRAM进行配置来实现。在数据移位寄存工作模式下,CSRAM的带控制端的传输门M1、M2配置为导通状态,该导通状态由与该控制端相连接cs1和cs2的外部CSRAM值决定,即所述配置信息存储CSRAM块中存储的配置信息决定。

本发明中所述2n位移位寄存器所使用的CSRAM,是在上述CSRAM结构的基础上,在输入端增加了一个带门控开关缓冲器BUF,带门控开关缓冲器BUF的输出端与所述CSRAM的io1相连,如图3所示。

图4为本发明中2n位移位寄存器所采用的移位寄存器单元的内部结构,采用图3中的两个带门控开关缓冲器BUF的CSRAM进行串联,时钟端clk与第一级BUF1的输入端en1直接连接并与第二级BUF2的en2通过一个反相器进行连接,前一级CSRAM的输出端OUT与后一级BUF2的输入端IN2相连;在时钟信号的控制下,数据将从第一级带门控开关缓冲器BUF的CSRAM的D端口即BUF1的输入端IN1输入,第二级带门控开关缓冲器BUF的CSRAM的输出端口即CSRAM2的输出端口io2为数据输出Q。图5为图4所描述的移位寄存器单元的外部逻辑结构示意图,其中D、clk端为均为输入端,Q端为输出端。

图6给出了本发明的移位长度可编程配置的移位寄存器的电路结构示意图,其中2n个移位寄存器单元均采用图5所示的电路结构。将2n个移位寄存器单元进行串连,具有n个输入端即An、An-1、An-2、...、A2、A1的LUT在BLE常规模式下被配置为MUX2n×1的多路选择开关功能,2n位移位寄存器的输出即Q2n、...、Q3、Q2、Q1与LUT相连接,通过LUT的n输入端选择2n位移位寄存器输出中的一位作为该MUX的OUT输出,移位寄存器中的数据可以在时钟脉冲作用下依次逐位移动,数据以串行输入IN端、串行输出到OUT端,可以实现1位至2n位即可变长度的移位寄存器操作。移位长度根据由CSRAM块控制的n输入端An、An-1、An-2、...、A2、A1的二进制值确定,如表1所示,当FPGA芯片进入配置状态,外部配置信号对CSRAM块进行配置并确定n输入端值,实现移位长度的选择和数据输出。如表1所示,当An、An-1、An-2、...、A2、A1配置为全0数值时,实现1位移位操作,选择Q1端作为OUT端输出;以此类推,该电路可通过配置实现1位至2n位即可变长度的移位寄存器操作。

表1LUT配置实现移位寄存器输出选择

以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

一种基于可编程基本逻辑单元的数据移位寄存电路专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0