专利摘要

本发明提供的非易失性存储器单元适用于Ⅲ族氮化物材料,且满足制备高密度全氮化物材料非易失性存储器件的要求。其中,Si3N4材料台面(7)作为阻抗开关层,实现存储功能。AlN材料台面(6)作为隧穿势垒层,缓解阻抗开关层(Si3N4材料台面)中存在的漏电通道对忆阻器稳定性的破坏,提升忆阻器的非易失性存储器开关过程的可靠性和状态稳定性。发展这种非易失性存储器单元,有望开发Ⅲ族氮化物半导体在发光、激光、光电探测以及高电子迁移率晶体管等应用领域之外的新用途,弥补其在存储器应用领域的空白,利于与氮化物半导体发光二极管、激光二极管、光电探测器以及高电子迁移率晶体管等实现基于全氮化物材料体系的单片光电集成。

权利要求

1.一种非易失性存储器单元,包括:

氮化物晶体管;

设置于所述氮化物晶体管上的氮化物金属-绝缘层-半导体忆阻器,所述氮化物金属-绝缘层-半导体忆阻器包括:Si掺杂的GaN材料台面(5),所述Si掺杂的GaN材料台面(5)附着于所述氮化物晶体管的AlGaN材料台面(4)上;附着于所述Si掺杂的GaN材料台面(5)上的AlN材料台面(6);附着于所述AlN材料台面(6)上的Si

漏极(11),所述漏极(11)的一端与Si掺杂的GaN材料台面(5)接触;所述漏极(11)的另一端与所述氮化物晶体管的GaN材料层(3)接触。

2.根据权利要求1所述的非易失性存储器单元,其特征在于,所述氮化物晶体管包括:衬底(1)、附着于所述衬底(1)上的GaN材料层(3)、附着于所述GaN材料层(3)上的AlGaN材料台面(4)、设置于所述AlGaN材料台面(4)上的栅极(9)、设置于所述GaN材料层(3)上的源极(10)。

3.根据权利要求2所述的非易失性存储器单元,其特征在于,所述漏极(11)的另一端贯穿于所述氮化物晶体管的所述AlGaN材料台面(4),并且与所述GaN材料层(3)接触。

4.根据权利要求1所述的非易失性存储器单元,其特征在于,所述AlGaN材料台面(4)中,Al的摩尔含量为10%~40%;

所述AlGaN材料台面(4)的厚度为5~20nm。

5.根据权利要求1所述的非易失性存储器单元,其特征在于,所述Si掺杂的GaN材料台面(5)中,Si的电子浓度介于10

所述Si掺杂的GaN材料台面(5)的厚度为0.5~1μm。

6.根据权利要求1所述的非易失性存储器单元,其特征在于,所述AlN材料台面(6)的厚度为1~3nm;所述Si

7.根据权利要求1所述的非易失性存储器单元,其特征在于,根据权利要求1所述的非易失性存储器单元,其特征在于,所述金属电极(8)为Ni、Ti、In和Al中的一种或Ni、Ti、In和Al中的几种的合金。

8.一种非易失性存储器单元的制备方法,包括:

A)采用金属有机化学气相沉积法在氮化物晶体管上依次生长Si掺杂的GaN材料层(5')、AlN材料层(6')、Si

B)采用光刻工艺对所述Si

C)采用光刻工艺对所述Si

D)采用电子束蒸发和光刻工艺,在Si掺杂的GaN材料台面(5)和氮化物晶体管的GaN材料层(3)上制作漏极(11),在所述Si

9.根据权利要求8所述的制备方法,其特征在于,步骤A)中,所述AlN材料层(6')和Si

10.一种非易失性存储器,包括权利要求1~7任意一项所述的非易失性存储器单元或权利要求8~9任意一项所述的制备方法制得的非易失性存储器单元。

说明书

技术领域

本发明涉及微电子材料与器件应用领域,具体涉及一种非易失性存储器单元、其制备方法及非易失性存储器。

背景技术

作为第三代半导体材料,Ⅲ族氮化物半导体已经在蓝、绿发光二极管、激光二极管、紫外光电探测器、高电子迁移率晶体管和高功率场效应管等光电子和微电子领域得到了广泛的发展和应用。然而,基于Ⅲ族氮化物材料的非易失性存储器件的发展相对滞后,目前仍然缺乏合理的存储器件结构,严重制约了高密度全氮化物材料非易失性存储器件的发展。因此,发展高密度全氮化物材料非易失性存储器,有望发挥Ⅲ族氮化物半导体在发光、激光、光电探测以及高电子迁移率晶体管领域的优势,弥补其应用领域的空白,实现基于全氮化物材料体系的单片光电集成。而这对于目前处于主导地位的硅基材料也是一种技术补充。因为单片光电集成中,作为光源的发光器件、光电转换的光探测器件、信息存储的存储器以及各种晶体管等电子元件是要求在同一衬底上的,而硅基材料属于间接带隙材料,因此,并不利于发展发光器件。

近年来,区别于传统基于电荷存储的非易失性存储器件,发展出了一种基于阻抗开关特性原理制成的新型的非易失性存储器件,称为忆阻器。这种忆阻器具有结构简单、擦写速度快、集成度高以及尺寸延展性好等优点。目前实现阻抗开关特性的结构主要包括金属-绝缘层-金属(MIM)和金属-绝缘层-半导体(MIS)两种。而MIM结构忆阻器件对于采用金属有机化学气相沉积技术制备的Ⅲ族氮化物材料并不适用。因此,设计出合理的存储器件结构,对于发展高密度全氮化物材料非易失性存储器件具有深远的意义。

发明内容

有鉴于此,本发明要解决的技术问题在于提供一种非易失性存储器单元、其制备方法及非易失性存储器,其适用于Ⅲ族氮化物材料,且满足制备高密度全氮化物材料非易失性存储器件的要求。

本发明提供了一种非易失性存储器单元,包括:

氮化物晶体管;

设置于所述氮化物晶体管上的氮化物金属-绝缘层-半导体忆阻器,所述氮化物金属-绝缘层-半导体忆阻器包括:Si掺杂的GaN材料台面(5),所述Si掺杂的GaN材料台面(5)附着于所述氮化物晶体管的AlGaN材料台面(4)上;附着于所述Si掺杂的GaN材料台面(5)上的AlN材料台面(6);附着于所述AlN材料台面(6)上的Si3N4材料台面(7);设置于所述Si3N4材料台面(7)上的金属电极(8);

漏极(11),所述漏极(11)的一端与Si掺杂的GaN材料台面(5)接触;所述漏极(11)的另一端与所述氮化物晶体管的GaN材料层(3)接触。

优选的,所述氮化物晶体管包括:衬底(1)、附着于所述衬底(1)上的GaN材料层(3)、附着于所述GaN材料层(3)上的AlGaN材料台面(4)、设置于所述AlGaN材料台面(4)上的栅极(9)、设置于所述GaN材料层(3)上的源极(10)。

优选的,所述漏极(11)的另一端贯穿于所述氮化物晶体管的所述AlGaN材料台面(4),并且与所述GaN材料层(3)接触。

优选的,所述AlGaN材料台面(4)中,Al的摩尔含量为10%~40%;

所述AlGaN材料台面(4)的厚度为5~20nm。

优选的,所述Si掺杂的GaN材料台面(5)中,Si的电子浓度介于10

所述Si掺杂的GaN材料台面(5)的厚度为0.5~1μm。

优选的,所述AlN材料台面(6)的厚度为1~3nm;所述Si3N4材料台面(7)的厚度为5~20nm。

优选的,根据权利要求1所述的非易失性存储器单元,其特征在于,所述金属电极(8)为Ni、Ti、In和Al中的一种或Ni、Ti、In和Al中的几种的合金。

本发明还提供了一种非易失性存储器单元的制备方法,包括:

A)采用金属有机化学气相沉积法在氮化物晶体管上依次生长Si掺杂的GaN材料层(5')、AlN材料层(6')、Si3N4材料层(7'),得到全氮化物半导体材料;

B)采用光刻工艺对所述Si3N4材料层(7')进行掩膜,得到Si3N4材料台面(7)和AlN材料台面(6);

C)采用光刻工艺对所述Si3N4材料台面(7)和Si掺杂的GaN材料层(5')进行掩膜,得到Si掺杂的GaN材料台面(5);

D)采用电子束蒸发和光刻工艺,在Si掺杂的GaN材料台面(5)和氮化物晶体管的GaN材料层(3)上制作漏极(11),在所述Si3N4材料台面(7)上制作金属电极(8),得到非易失性存储器单元。

优选的,步骤A)中,所述AlN材料层(6')和Si3N4材料层(7')的生长还可以采用等离子体增强化学气相沉积法或射频磁控溅射法。

本发明还提供了一种非易失性存储器,包括上文所述的非易失性存储器单元或上文所述的制备方法制得的非易失性存储器单元。

本发明提供了一种非易失性存储器单元,包括:

氮化物晶体管;

设置于所述氮化物晶体管上的氮化物金属-绝缘层-半导体忆阻器,所述氮化物金属-绝缘层-半导体忆阻器包括:Si掺杂的GaN材料台面(5),所述Si掺杂的GaN材料台面(5)附着于所述氮化物晶体管的AlGaN材料台面(4)上;附着于所述Si掺杂的GaN材料台面(5)上的AlN材料台面(6);附着于所述AlN材料台面(6)上的Si3N4材料台面(7);设置于所述Si3N4材料台面(7)上的金属电极(8);

漏极(11),所述漏极(11)的一端与Si掺杂的GaN材料台面(5)接触;所述漏极(11)的另一端与所述氮化物晶体管的GaN材料层(3)接触。

本发明提供的非易失性存储器单元适用于Ⅲ族氮化物材料,且满足制备高密度全氮化物材料非易失性存储器件的要求。其中,Si3N4材料台面(7)作为阻抗开关层,实现非易失性存储器的高阻态和低阻态的状态变化,从而实现存储功能。AlN材料台面(6)作为隧穿势垒层,作用是缓解阻抗开关层(Si3N4材料台面)中存在的漏电通道对忆阻器稳定性的破坏,进一步提升忆阻器的非易失性存储器开关过程的可靠性和状态稳定性。发展这种非易失性存储器单元,有望开发Ⅲ族氮化物半导体在发光、激光、光电探测以及高电子迁移率晶体管等应用领域之外的新用途,弥补其在存储器应用领域的空白,也有利于与氮化物半导体发光二极管、激光二极管、光电探测器以及高电子迁移率晶体管等实现基于全氮化物材料体系的单片光电集成,意义重大。

实验结果表明,本发明提供的非易失性存储器单元的高阻态和低阻态开关切换次数超过10

附图说明

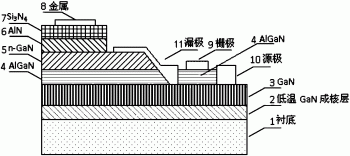

图1为本发明的一个实施例提供的非易失性存储器单元的结构示意图;

图2为本发明得到的全氮化物半导体材料的结构示意图。

具体实施方式

下面将结合本发明实施例,对本发明的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

本发明提供了一种非易失性存储器单元,包括:

氮化物晶体管;

设置于所述氮化物晶体管上的氮化物金属-绝缘层-半导体忆阻器,所述氮化物金属-绝缘层-半导体忆阻器包括:Si掺杂的GaN材料台面(5),所述Si掺杂的GaN材料台面(5)附着于所述氮化物晶体管的AlGaN材料台面(4)上;附着于所述Si掺杂的GaN材料台面(5)上的AlN材料台面(6);附着于所述AlN材料台面(6)上的Si3N4材料台面(7);设置于所述Si3N4材料台面(7)上的金属电极(8);

漏极(11),所述漏极(11)的一端与Si掺杂的GaN材料台面(5)接触;所述漏极(11)的另一端与所述氮化物晶体管的GaN材料层(3)接触。

所述氮化物金属-绝缘层-半导体忆阻器包括Si掺杂的GaN材料台面(5),所述Si掺杂的GaN材料台面(5)附着于AlGaN材料台面(4)上。Si掺杂的GaN材料台面(5)作为金属-绝缘层-半导体(MIS)结构忆阻器的半导体层(S),是双端元件忆阻器的一端。所述Si掺杂的GaN材料台面(5)中,Si的电子浓度优选介于10

所述氮化物金属-绝缘层-半导体忆阻器包括AlN材料台面(6),所述AlN材料台面(6)附着于所述Si掺杂的GaN材料台面(5)上。所述AlN材料台面(6)的厚度优选为1~3nm。在本发明中,所述AlN材料台面(6)为隧穿势垒层,无需像现有技术那样需要较厚的厚度,仅仅薄薄的一层的AlN材料台面(6)就能够缓解阻抗开关层(Si3N4材料台面)中存在的漏电通道对忆阻器稳定性的破坏,进一步提升忆阻器的非易失性存储器开关过程的可靠性和状态稳定性。

所述氮化物金属-绝缘层-半导体忆阻器包括Si3N4材料台面(7),所述Si3N4材料台面(7)附着于所述AlN材料台面(6)上。Si3N4材料台面(7)作为阻抗开关层,实现非易失性存储器的高阻态和低阻态的状态变化,从而实现存储功能。所述Si3N4材料台面(7)的厚度优选为5~20nm。

所述氮化物金属-绝缘层-半导体忆阻器还包括金属电极(8),所述金属电极(8)设置于所述Si3N4材料台面(7)上。所述金属电极(8)优选为Ni、Ti、In和Al中的一种或Ni、Ti、In和Al中的几种的合金。

在本发明中,所述氮化物晶体管优选包括:衬底(1)、附着于所述衬底(1)上的GaN材料层(3)、附着于所述GaN材料层(3)上的AlGaN材料台面(4)、设置于所述AlGaN材料台面(4)上的栅极(9)、设置于所述GaN材料层(3)上的源极(10)。

所述氮化物晶体管优选包括衬底(1),所述衬底(1)优选为单面抛光衬底、双面抛光蓝宝石衬底或GaN单晶衬底。

所述衬底(1)为单面抛光衬底或双面抛光蓝宝石衬底时,所述非易失性存储器单元优选还包括低温GaN成核层(2);所述低温GaN成核层(2)附着于所述衬底(1)上,所述GaN材料层(3)附着于所述低温GaN成核层(2)上。本发明对所述衬底(1)的厚度并无特殊的限制,采用本领域技术人员熟知的衬底的厚度即可。所述低温GaN成核层(2)的厚度优选为30~50nm。

所述氮化物晶体管优选还包括所述GaN材料层(3),所述GaN材料层(3)附着于所述衬底(1)上。所述GaN材料层(3)的厚度优选为2~5μm。

所述氮化物晶体管优选还包括所述AlGaN材料台面(4),所述AlGaN材料台面(4)附着于所述GaN材料层(3)上。所述AlGaN材料台面(4)中,Al的摩尔含量优选为10%~40%。所述AlGaN材料台面(4)的厚度优选为5~20nm。

所述氮化物晶体管优选还包括栅极(9),所述栅极(9)设置于所述AlGaN材料台面(4)上。所述栅极(9)优选为Ni/Au多层电极。

所述氮化物晶体管优选还包括源极(10),所述源极(10)优选为Ti/Al/Ni/Au多层电极。

在本发明中,所述非易失性存储器单元还包括漏极(11)。所述漏极(11)的一端与Si掺杂的GaN材料台面(5)接触;所述漏极(11)的另一端与所述氮化物晶体管的GaN材料层(3)接触。

优选的,所述漏极(11)的一端与Si掺杂的GaN材料台面(5)接触;所述漏极(11)的另一端贯穿于所述氮化物晶体管的AlGaN材料台面(4),并且与所述氮化物晶体管的GaN材料层(3)接触。

所述漏极(11)优选为Ti/Al/Ni/Au多层电极。

参见图1,图1为本发明的一个实施例提供的非易失性存储器单元的结构示意图;其中,1为衬底;2为低温GaN成核层;3为GaN材料层;4为AlGaN材料台面;5为Si掺杂的GaN材料台面;6为AlN材料台面;7为Si3N4材料台面;8为金属电极;9为栅极;10为源极;11为漏极。

本发明还提供了一种非易失性存储器单元的制备方法,包括:

A)采用金属有机化学气相沉积法在氮化物晶体管上依次生长Si掺杂的GaN材料层(5')、AlN材料层(6')、Si3N4材料层(7'),得到全氮化物半导体材料;

B)采用光刻工艺对所述Si3N4材料层(7')进行掩膜,得到Si3N4材料台面(7)和AlN材料台面(6);

C)采用光刻工艺对所述Si3N4材料台面(7)和Si掺杂的GaN材料层(5')进行掩膜,得到Si掺杂的GaN材料台面(5);

D)采用电子束蒸发和光刻工艺,在Si掺杂的GaN材料台面(5)和氮化物晶体管的GaN材料层(3)上制作漏极(11),在所述Si3N4材料台面(7)上制作金属电极(8),得到非易失性存储器单元。

优选的,具体为:

a)采用金属有机化学气相沉积法在衬底(1)上依次生长GaN材料层(3)、AlGaN材料层(4')、Si掺杂的GaN材料层(5')、AlN材料层(6')、Si3N4材料层(7'),得到全氮化物半导体材料;

b)采用光刻工艺对所述Si3N4材料层(7')进行掩膜,得到Si3N4材料台面(7)和AlN材料台面(6);

c)采用光刻工艺对所述Si3N4材料台面(7)和Si掺杂的GaN材料层(5')进行掩膜,得到Si掺杂的GaN材料台面(5);

d)采用光刻工艺对所述Si3N4材料台面(7)、所述的Si掺杂的GaN材料台面(5)和AlGaN材料层(4')进行掩膜,得到AlGaN材料台面(4);

e)采用电子束蒸发和光刻工艺,在Si掺杂的GaN材料台面(5)和氮化物晶体管的GaN材料层(3)上制作漏极(11),在GaN材料层(3)上制作源极(10),在AlGaN材料台面(4)上制作栅极(9),在Si3N4材料台面(7)上制作金属电极(8),得到非易失性存储器单元。

本发明采用金属有机化学气相沉积法在衬底(1)上依次生长GaN材料层(3)、AlGaN材料层(4')、Si掺杂的GaN材料层(5')、AlN材料层(6')、Si3N4材料层(7'),得到全氮化物半导体材料。

所述衬底(1)优选为单面抛光衬底、双面抛光蓝宝石衬底或GaN单晶衬底。当所述衬底(1)为单面抛光衬底或双面抛光蓝宝石衬底时,采用金属有机化学气相沉积法在衬底(1)上依次生长低温GaN成核层(2)、GaN材料层(3)、AlGaN材料层(4')、Si掺杂的GaN材料层(5')、AlN材料层(6')、Si3N4材料层(7'),得到全氮化物半导体材料。所述全氮化物半导体材料的结构如图2所示。图2为本发明得到的全氮化物半导体材料的结构示意图;其中,1为衬底;2为低温GaN成核层;3为GaN材料层;4'为AlGaN材料层;5'为Si掺杂的GaN材料层;6'为AlN材料层;7'为Si3N4材料层;8为金属电极;9为栅极;10为源极;11为漏极。

所述低温GaN成核层(2)的厚度优选为30~50nm。所述GaN材料层(3)的厚度优选为2~5μm。

本发明对所述金属有机化学气相沉积法的工艺参数并无特殊的限制,采用本领域技术人员熟知的工艺参数即可。

在本发明中,所述AlN材料层(6')和Si3N4材料层(7')的生长还可以采用等离子体增强化学气相沉积法或射频磁控溅射法。本发明对所述等离子体增强化学气相沉积法的工艺参数并无特殊的限制,采用本领域技术人员熟知的工艺参数即可。在本发明的某些实施例中,所述等离子体增强化学气相沉积法制备Si3N4材料层(7')工艺参数为:SiH4流量40sccm,NH3流量8sccm,衬底温度300℃。本发明对所述射频磁控溅射法的工艺参数并无特殊的限制,采用本领域技术人员熟知的工艺参数即可。在本发明的某些实施例中,所述射频磁控溅射法制备AlN材料层(6')的工艺参数为:采用AlN靶材,在2×10

然后,采用光刻工艺对所述Si3N4材料层(7')进行掩膜,得到Si3N4材料台面(7)和AlN材料台面(6)。本发明对所述光刻工艺的参数并无特殊的限制,采用本领域技术人员熟知的光刻工艺的参数即可。

所述Si3N4材料台面(7)的厚度优选为5~20nm。Si3N4材料台面(7)作为阻抗开关层,实现非易失性存储器的高阻态和低阻态的状态变化,从而实现存储功能。所述AlN材料台面(6)的厚度优选为1~3nm。在本发明中,所述AlN材料台面(6)为隧穿势垒层,无需像现有技术那样需要较厚的厚度,仅仅薄薄的一层的AlN材料台面(6)就能够缓解阻抗开关层(Si3N4材料台面)中存在的漏电通道对忆阻器稳定性的破坏,进一步提升忆阻器的非易失性存储器开关过程的可靠性和状态稳定性。

采用光刻工艺对所述Si3N4材料台面(7)和Si掺杂的GaN材料层(5')进行掩膜,得到Si掺杂的GaN材料台面(5)。本发明对所述光刻工艺的参数并无特殊的限制,采用本领域技术人员熟知的光刻工艺的参数即可。

所述Si掺杂的GaN材料台面(5)中,Si的电子浓度优选介于10

采用光刻工艺对所述Si3N4材料台面(7)、所述的Si掺杂的GaN材料台面(5)和AlGaN材料层(4')进行掩膜,得到AlGaN材料台面(4)。本发明对所述光刻工艺的参数并无特殊的限制,采用本领域技术人员熟知的光刻工艺的参数即可。

所述AlGaN材料台面(4)中,Al的摩尔含量优选为10%~40%。所述AlGaN材料台面(4)的厚度优选为5~20nm。

再采用电子束蒸发和光刻工艺相结合的工艺,在Si掺杂的GaN材料台面(5)和氮化物晶体管的GaN材料层(3)上制作漏极(11),在GaN材料层(3)上制作源极(10),在AlGaN材料台面(4)上制作栅极(9),在Si3N4材料台面(7)上制作金属电极(8),得到非易失性存储器单元。本发明对所述电子束蒸发的参数并无特殊的限制,采用本领域技术人员熟知的电子束蒸发的参数即可。本发明对所述光刻工艺的参数并无特殊的限制,采用本领域技术人员熟知的光刻工艺的参数即可。

所述电子束蒸发和光刻工艺相结合的工艺之后,优选还包括退火处理。所述退火处理的作用是使得漏极(11)与Si掺杂的GaN材料层(5)形成欧姆接触。本发明对所述退火处理的参数并无特殊的限制,采用本领域技术人员熟知的退火处理的参数即可。

在本发明中,所述金属电极(8)优选为Ni、Ti、In和Al中的一种或Ni、Ti、In和Al中的几种的合金。所述栅极(9)优选为Ni/Au多层电极。所述源极(10)优选为Ti/Al/Ni/Au多层电极。

所述漏极(11)的一端与Si掺杂的GaN材料台面(5)接触;所述漏极(11)的另一端与所述氮化物晶体管的GaN材料层(3)接触。优选的,所述漏极(11)的一端与Si掺杂的GaN材料台面(5)接触;所述漏极(11)的另一端贯穿于所述氮化物晶体管的AlGaN材料台面(4),并且与所述氮化物晶体管的GaN材料层(3)接触。所述漏极(11)优选为Ti/Al/Ni/Au多层电极。

本发明对上述所采用的原料组分的来源并无特殊的限制,可以为一般市售。

本发明还提供了一种非易失性存储器,包括上文所述的非易失性存储器单元或上文所述的制备方法制得的非易失性存储器单元。

所述非易失性存储器单元在形成非易失性存储器时,字线与所述栅极(9)对应,位线与所述源极(10)对应;脉冲控制线与所述漏极(11)对应。

本发明提供了一种非易失性存储器单元,包括:

氮化物晶体管;

设置于所述氮化物晶体管上的氮化物金属-绝缘层-半导体忆阻器,所述氮化物金属-绝缘层-半导体忆阻器包括:Si掺杂的GaN材料台面(5),所述Si掺杂的GaN材料台面(5)附着于所述氮化物晶体管的AlGaN材料台面(4)上;附着于所述Si掺杂的GaN材料台面(5)上的AlN材料台面(6);附着于所述AlN材料台面(6)上的Si3N4材料台面(7);设置于所述Si3N4材料台面(7)上的金属电极(8);

漏极(11),所述漏极(11)的一端与Si掺杂的GaN材料台面(5)接触;所述漏极(11)的另一端与所述氮化物晶体管的GaN材料层(3)接触。

本发明提供的非易失性存储器单元适用于Ⅲ族氮化物材料,且满足制备高密度全氮化物材料非易失性存储器件的要求。其中,Si3N4材料台面(7)作为阻抗开关层,实现非易失性存储器的高阻态和低阻态的状态变化,从而实现存储功能。AlN材料台面(6)作为隧穿势垒层,作用是缓解阻抗开关层(Si3N4材料台面)中存在的漏电通道对忆阻器稳定性的破坏,进一步提升忆阻器的非易失性存储器开关过程的可靠性和状态稳定性。发展这种非易失性存储器单元,有望开发Ⅲ族氮化物半导体在发光、激光、光电探测以及高电子迁移率晶体管等应用领域之外的新用途,弥补其在存储器应用领域的空白,也有利于与氮化物半导体发光二极管、激光二极管、光电探测器以及高电子迁移率晶体管等实现基于全氮化物材料体系的单片光电集成,意义重大。

实验结果表明,本发明提供的非易失性存储器单元的高阻态和低阻态开关切换次数超过10

为了进一步说明本发明,下面结合实施例对本发明提供的一种非易失性存储器单元、其制备方法及非易失性存储器进行详细地描述,但不能将它们理解为对本发明保护范围的限定。

以下实施例中所用的原料均为市售。

实施例1

采用金属有机化学气相沉积法在单面抛光衬底(1)上依次生长低温GaN成核层(2)、GaN材料层(3)、AlGaN材料层(4')、Si掺杂的GaN材料层(5')、AlN材料层(6')、Si3N4材料层(7'),得到全氮化物半导体材料。所述低温GaN成核层(2)的厚度为35nm,所述GaN材料层(3)的厚度为3μm。

然后,采用光刻工艺对所述Si3N4材料层(7')进行掩膜,得到厚度为20nm的Si3N4材料台面(7)和厚度为3nm的AlN材料台面(6)。

采用光刻工艺对所述Si3N4材料台面(7)和Si掺杂的GaN材料层(5')进行掩膜,得到厚度为1μm的Si掺杂的GaN材料台面(5)。所述Si掺杂的GaN材料台面(5)中,Si掺杂的GaN的电子浓度为5×10

采用光刻工艺对所述Si3N4材料台面(7)、所述的Si掺杂的GaN材料台面(5)和AlGaN材料层(4')进行掩膜,得到厚度为20nm的AlGaN材料台面(4)。所述AlGaN材料台面(4)中,Al的摩尔含量为40%。

再采用电子束蒸发和光刻工艺相结合的工艺,经退火处理后,在Si掺杂的GaN材料台面(5)和氮化物晶体管的GaN材料层(3)上制作漏极(11),在GaN材料层(3)上制作源极(10),在AlGaN材料台面(4)上制作栅极(9),在Si3N4材料台面(7)上制作金属电极(8),得到非易失性存储器单元。所述金属电极为Ni电极,所述栅极(9)为Ni/Au多层电极,所述源极(10)为Ti/Al/Ni/Au多层电极,所述漏极(11)为Ti/Al/Ni/Au多层电极。

将制得的非易失性存储器单元制成非易失性存储器,字线与所述栅极(9)对应,位线与所述源极(10)对应;脉冲控制线与所述漏极(11)对应。

实验结果表明,本实施例提供的非易失性存储器单元的高阻态和低阻态开关切换次数超过10

实施例2

采用金属有机化学气相沉积法在GaN单晶衬底(1)上依次生长GaN材料层(3)、AlGaN材料层(4')、Si掺杂的GaN材料层(5')、AlN材料层(6')、Si3N4材料层(7'),得到全氮化物半导体材料。所述GaN材料层(3)的厚度为3μm。

然后,采用光刻工艺对所述Si3N4材料层(7')进行掩膜,得到厚度为20nm的Si3N4材料台面(7)和厚度为3nm的AlN材料台面(6)。

采用光刻工艺对所述Si3N4材料台面(7)和Si掺杂的GaN材料层(5')进行掩膜,得到厚度为1μm的Si掺杂的GaN材料台面(5)。所述Si掺杂的GaN材料台面(5)中,Si掺杂的GaN的电子浓度为5×10

采用光刻工艺对所述Si3N4材料台面(7)、所述的Si掺杂的GaN材料台面(5)和AlGaN材料层(4')进行掩膜,得到厚度为20nm的AlGaN材料台面(4)。所述AlGaN材料台面(4)中,Al的摩尔含量为40%。

再采用电子束蒸发和光刻工艺相结合的工艺,经退火处理后,在Si掺杂的GaN材料台面(5)和氮化物晶体管的GaN材料层(3)上制作漏极(11),在GaN材料层(3)上制作源极(10),在AlGaN材料台面(4)上制作栅极(9),在Si3N4材料台面(7)上制作金属电极(8),得到非易失性存储器单元。所述金属电极为Ni电极,所述栅极(9)为Ni/Au多层电极,所述源极(10)为Ti/Al/Ni/Au多层电极,所述漏极(11)为Ti/Al/Ni/Au多层电极。

将制得的非易失性存储器单元制成非易失性存储器,字线与所述栅极(9)对应,位线与所述源极(10)对应;脉冲控制线与所述漏极(11)对应。

实验结果表明,本实施例提供的非易失性存储器单元的高阻态和低阻态开关切换次数超过10

对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

一种非易失性存储器单元、其制备方法及非易失性存储器专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0