IPC分类号 : H04B1/16,H03F3/45,H03G1/00,H03D7/16,H03H1/02

专利摘要

本发明公开了一种具有多种增益模式、能自动调谐的射频接收前端,其包括:低噪声放大器,其输入端连接输入信号,输出端采用数控电阻作为负载来校准增益;混频器,其I路混频器和Q路混频器的差分输入端均连接到低噪声放大器的输出端,其差分输出端均连接到复数滤波器的差分输入端;复数滤波器,采用多级级联结构,通过数控电阻实现多种增益模式,同时时间常数可通过控制电容阵列来实现调谐;时间常数校正电路,其输出端连接复数滤波器的校正控制字输入端。本发明中的射频接收前端将电流模低噪声放大器、无源混频器和有源RC复数滤波器组合在一起,具有低噪声、高线性度、低功耗、低成本等优点。

说明书

技术领域技术领域

本发明涉及射频接收前端技术领域,特别涉及一种具有多种增益模式的、能自动调谐的射频接收前端。

技术背景背景技术

在射频接收机中,很多应用往往要求接收信号能有很大的动态范围,即具备较小的接收灵敏度、较强的抗大信号饱和能力以及较高的线性度。而射频接收机的接收前端的噪声系数直接决定接收机的接收灵敏度,接收前端的增益和结构决定接收机的抗大信号饱和能力和线性度。在CMOS(Complementary Metal Oxide Semiconductor)工艺下,电阻和电容会随着工艺、温度而偏差,这会严重影响接收机的性能,特别是采用有源RC(Resistor-Capacitor)滤波器的接收机,电阻和电容的偏差影响滤波器的性能,进而会影响整个接收机的性能。

关于接收前端的组合方式,一般都是采用低噪声放大器、混频器、滤波器组成,例如采用电压模的低噪声放大器、吉尔波特混频器和有源RC复数滤波器组成,但吉尔波特混频器线性度差,会影响整个接收机的动态范围。

对于低噪声放大器的增益控制,其设计对接收机的噪声性能影响很大,所以很多传统的接收机并没有在低噪声放大器上做增益控制,而是在后级电路中做分档,这样设计的低噪声放大器动态范围很小,进而导致接收机的动态范围小。还有的采用两个或两个以上的低噪声放大器交替工作来适应不同的输入信号强度,例如,采用两个低噪声放大器,对小的输入信号两个同时起用,对比较大的输入信号将第二个旁路掉。再例如,采用两个低噪声放大器和一个切换开关,对应不同的输入信号进行切换,这样做的缺点是面积大、功耗大。还有的对共源共栅低噪声放大器的共栅管采用多个并联的结构进行增益控制,例如,采用三路共栅管并联来实现增益控制,但缺点是动态范围很小,抗大信号饱和能力差。还有的采用共栅输入的低噪声放大器,在输入端做增益控制,例如,采用共栅输入的低噪声放大器,在输入端做增益控制,在两个共栅放大管之间也做了增益控制,但增益低、噪声性能差。

关于接收前端中的滤波器,很多采用有源RC滤波器,具有高的动态范围和线性度。而针对有源RC滤波器中电阻和电容会随工艺和温度而偏差的问题,有的提出了校正的方法,例如,有文献披露了一种校正RC时间常数的电路,但并没给出对RC滤波器的具体校正方法和电路的连接方式,也没有给出合理快速的校正算法。并且目前也没有人给出电容阵列的有效实施方法,传统的方法是采用NMOS管、PMOS管或CMOS传输门做开关,直接与电容串联,但当开关关断时开关与电容的连接点处的直流电平不确定,这会造成开关在很多时候不能有效的关断,致使电容阵列的总电容值不准确,严重影响滤波器的性能。

发明内容发明内容

本发明的目的是提供一种具有多增益模式、而且能够自动调谐有源RC滤波器时间常数的射频接收前端,包括多增益模式的低噪声放大器与数控增益的复数滤波器相结合以实现高动态范围。

为达到上述目的,提供一种依照本发明实施方式的具有多种增益模式、能自动调谐的射频接收前端,其包括:

低噪声放大器,采用电感源极负反馈、共源共栅放大的结构,分别在输入共源放大管的栅极、输入共源放大管的漏极做添加增益控制开关,其输入端连接输入信号,输出端采用数控电阻作为负载来校准增益;

混频器,包括I路混频器和Q路混频器,其差分输入端均连接到低噪声放大器的输出端,其差分输出端均连接到复数滤波器的差分输入端;

复数滤波器,采用多级级联结构,各级的增益控制字输入端相连,各级的电容阵列控制字输入端相连;

时间常数校正电路,其输出端连接复数滤波器的校正控制字输入端,用于对复数滤波器的RC时间常数随工艺、温度产生的变化进行校正。

优选地,所述低噪声放大器包括:

四个PMOS管,各个PMOS管的源极接在电源正电压上,各个PMOS管的栅极连接到增益控制字,第一PMOS管和第二PMOS管的栅极相连后连接到第一增益控制字,第三PMOS管和第四PMOS管的栅极相连后连接到第二增益控制字;

八个NMOS管,第一NMOS管和第二NMOS管作为低噪声放大器的共源放大管,第一NMOS管的栅极连接第一偏置电压输入端,第二NMOS管的栅极连接到第二偏置电压输入端;第三NMOS管、第四NMOS管和第五NMOS管组成输入端增益控制开关,第四NMOS管的漏极连接到第三NMOS管的漏极,第五NMOS管的漏极连接到第三NMOS管的源极,第四NMOS管的源极和第五NMOS管的源极均接地,第三NMOS管、第四NMOS管、第五NMOS管的栅极相连后连接到第三增益控制字;第六NMOS管在输入共源放大管的漏极作增益控制用,第六NMOS管的漏极连接到第一NMOS管的漏极,第六NMOS管的源极连接到第二NMOS管的漏极,第六NMOS管的栅极连接到第四增益控制字;第七NMOS管和第八NMOS管为共栅放大管,第七NMOS管的源极连接到第一NMOS管的漏极,第八NMOS管的源极连接到第二NMOS管的漏极,第七NMOS管的栅极和第八NMOS管的栅极相连后连接到第三偏置电压端;

四个电感,第一电感连接同相输入端口和第四NMOS管的漏极,第二电感连接反相输入端口和第五NMOS管的漏极,第三电感连接第一NMOS管的源极和地,第四电感连接第二NMOS管的源极和地;

两个电容,第一电容连接第四NMOS管的漏极和第一偏置电压,第二电容连接第五NMOS管的漏极和第二偏置电压;

四个电阻,第一电阻连接第一PMOS管的漏极和第七NMOS管的漏极,第二电阻连接第二PMOS管的漏极和第八NMOS管的漏极,第三电阻连接第三PMOS管的漏极和第七NMOS管的漏极,第四电阻连接第四PMOS管的漏极和第八NMOS管的漏极。

优选地,所述混频器包括:

一个运算放大器,运算放大器的差分输出端连接到混频器的差分输出端;

一个能隙基准源,用于提供各个偏置电压;

四个NMOS管,第一NMOS管的源极和第二NMOS管的源极相连,第一NMOS管的漏极与第三NMOS管的漏极相连后连接到运算放大器的同相输入端,第三NMOS管的源极与第四NMOS管的源极相连,第二NMOS管的漏极与第四NMOS管的漏极相连后连接到运算放大器的反相输入端,第一NMOS管的栅极与第四NMOS管的栅极相连,第二NMOS管的栅极与第三NMOS管的栅极相连;

四个电容,第一电容连接运算放大器的同相输入端和反相输出端,第二电容连接运算放大器的反相输入端和同相输出端,第三电容连接运算放大器的同相输入端和地,第四电容连接运算放大器的反相输入端和地,第五电容连接第一NMOS管的源极和混频器的同相输入端,第六电容连接第三NMOS管的源极和混频器的反相输入端,第七电容连接第一NMOS管的栅极和本振信号的同相输入端,第八电容连接第三NMOS管的栅极和本振信号的反相输入端;

八个电阻,第一电阻连接运算放大器的同相输入端和反相输出端,第二电阻连接运算放大器的反相输入端和同相输出端,第三电阻连接运算放大器的同相输入端和能隙基准源,第四电阻连接运算放大器的反相输入端和能隙基准源,第五电阻连接第一NMOS管的栅极和能隙基准源,第六电阻连接第一NMOS管的源极和能隙基准源,第七电阻连接第二NMOS管的栅极和能隙基准源,第八电阻连接第三NMOS管的源极和能隙基准源。

优选地,所述复数滤波器的第一级复数滤波器单元的差分输入端连接到复数滤波器的差分输入端,中间每一级复数滤波器单元的差分输入端连接到前一级的差分输出端,最后一级的差分输出端连接到复数滤波器的差分输出端。

优选地,复数滤波器各级的增益控制字输入端相连,各级的电容阵列控制字输入端相连。

优选地,所述复数滤波器包括:

两个运算放大器,第一运算放大器的差分输出连接复数滤波器的I路差分输出端,第二运算放大器的差分输出连接复数滤波器的Q路差分输出端;

四个电容阵列单元,第一电容阵列单元连接第一运算放大器的同相输入端和反相输出端,第二电容阵列单元连接第一运算放大器的反相输入端和同相输出端,第三电容阵列单元连接第二运算放大器的同相输入端和反相输出端,第四电容阵列单元连接第二运算放大器的反相输入端和同相输出端,四个电容阵列的电容阵列控制字输入端相连后连接到整个复数滤波器单元的电容阵列控制字输入端;

四个NMOS开关管,第一NMOS管的漏极连接到第一运算放大器的同相输入端,第二NMOS管的漏极连接到第一运算放大器的反相输入端,第三NMOS管的漏极连接到第二运算放大器的同相输入端,第四NMOS管的漏极连接到第二运算放大器的反相输入端,各个NMOS管的栅极连接后接到增益控制字输入端;

十六个电阻阵列,第一电阻阵列接第一运算放大器的同相输入端和反相输出端,第二电阻阵列连接第一运算放大器的反相输入端和同相输出端,第三电阻阵列连接第一运算放大器的反相输入端和第二运算放大器的反相输出端,第四电阻阵列连接第一运算放大器的同相输入端和第二运算放大器的同相输出端,第五电阻阵列连接第一运算放大器的反相输出端和第二运算放大器的同相输入端,第六电阻阵列连接第一运算放大器的同相输出端和第二运算放大器的反相输入端,第七电阻阵列连接第二运算放大器的同相输入端和反相输出端,第八电阻阵列连接第二运算放大器的反相输入端和同相输出端,第九电阻阵列连接第一NMOS管的源极和漏极,第十电阻阵列连接第二NMOS管的源极和漏极,第十一电阻阵列连接第三NMOS管的源极和漏极,第十二电阻阵列连接第四NMOS管的源极和漏极,第十三电阻阵列连接第一NMOS管的源极和复数滤波器单元的I路反相输入端,第十四电阻阵列连接第二NMOS管的源极和复数滤波器单元的I路同相输入端,第十五电阻阵列连接第三NMOS管的源极和复数滤波器单元的Q路反相输入端,第十六电阻阵列连接第四NMOS管的源极和复数滤波器单元的Q路同相输入端。

优选地,所述时间常数校正电路具体包括:

一个能隙基准源,用于给各个模块提供参考电压;

一个数字电路模块,用于进行数字校正;

四个运算放大器,第一运算放大器和第二运算放大器用作放大器,第三运算放大器和第四运算放大器用作电压比较器;第一运算放大器的同相输入端、第二运算放大器的同相输入端、第三运算放大器的同相输入端和第四运算放大器的反相输入端都连接到能隙基准源;第二运算放大器的输出端、第三运算放大器的反相输入端和第四运算放大器的同相输入端相连;

一个电阻阵列,连接第一运算放大器的反相输入端和地;

一个电容阵列单元,连接第二运算放大器的反相输入端和输出端,控制字输入端与数字电路模块相连后连接到整个时间常数校正电路的输出端;

两个NMOS管,第一NMOS管的栅极连接第一运算放大器的输出端,第一NMOS管的漏极连接第二运算放大器的反相输入端,第一NMOS管的源极连接第一运算放大器的反相输入端,第二NMOS管的源极连接第二运算放大器的反相输入端,第二NMOS管的漏极连接第二运算放大器的输出端,第二NMOS管的栅极连接数字模块。

优选地,所述电容阵列单元具体包括:

八个NMOS管做开关,第一NMOS管、第二NMOS管、第三NMOS管、第四NMOS管的源极相连后连接到电容阵列单元的第一输入端,第五NMOS管、第六NMOS管、第七NMOS管、第八NMOS管的漏极相连,第一NMOS管的漏极与第五NMOS管的源极相连,第二NMOS管的漏极与第六NMOS管的源极相连,第三NMOS管的漏极与第七NMOS管的源极相连,第四NMOS管的漏极与第八NMOS管的源极相连;第一NMOS管的栅极连接到控制字第一位的输入端,第二NMOS管的栅极连接到控制字第二位的输入端,第三NMOS管的栅极连接到控制字第三位的输入端,第四NMOS管的栅极连接到控制字第四位的输入端;

四个反相器,第一反相器的输入端连接第一NMOS管的栅极,第一反相器的输出端连接第五NMOS管的栅极,第二反相器的输入端连接第二NMOS管的栅极,第二反相器的输出端连接第六NMOS管的栅极,第三反相器的输入端连接第三NMOS管的栅极,第三反相器的输出端连接第七NMOS管的栅极,第四反相器的输入端连接第四NMOS管的栅极,第四反相器的输出端连接第八NMOS管的栅极;

四个电容,第一电容连接第一NMOS管的漏极和电容阵列单元的第二输入端,第二电容连接第二NMOS管的漏极和电容阵列单元的第二输入端,第三电容连接第三NMOS管的漏极和电容阵列单元的第二输入端,第四电容连接第四NMOS管的漏极和电容阵列单元的第二输入端;

两个电阻,第一电阻连接电源和第五NMOS管的漏极,第二电阻连接第五NMOS管的漏极和地。

上述技术方案具有如下优点:低噪声放大器在输入共源放大管的栅极和漏极同时做增益控制,并在输出端做增益校准,同时对复数滤波器做增益控制,这样一来,接收前端对小的输入信号具有高增益、低噪声,对大的输入信号具有强的抗大信号饱和能力,这显著提高了接收机的动态范围;采用无源的混频器与电流模低噪声放大器、有源RC复数滤波器配合使用,具有低噪声、高线性度的优点;对复数滤波器的RC时间常数进行自动校正,用一套校正电路实现所有电容阵列的校正,具有低功耗、低成本的优点,同时采用二分法校正,加快了校正速度。

附图说明附图说明

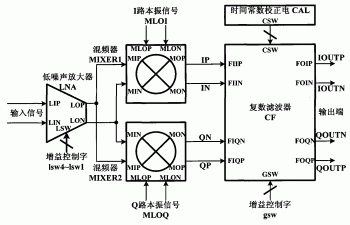

图1是本发明实施例的具有多种增益模式、能自动调谐的射频接收前端电路框图;

图2是本发明实施例的低噪声放大器的电路图;

图3是本发明实施例的混频器的电路图;

图4是本发明实施例的复数滤波器电路框图;

图5是本发明实施例的复数滤波器级联单元的电路图;

图6是本发明实施例的时间常数校正电路的电路图;

图7是本发明实施例的电容阵列单元的电路图。

具体实施方式具体实施方式

下面结合附图和实施例,对本发明的具体实施方式作进一步详细描述。以下实施例用于说明本发明,但不用来限制本发明的范围。

本发明实施例的具有多种增益模式的、能自动调谐的射频接收前端电路框图如图1所示,低噪声放大器LNA的差分输入LIP和LIN端连接到输入信号,低噪声放大器的增益控制端LSW连接到增益控制字lsw4~lsw1。I路混频器MIXER1和Q路混频器MIXER2的差分输入端MIP和MIN分别连接到LNA的差分输出端LOP和LON,I路混频器的本振信号差分输入端MLOP和MLON连接I路本振信号MLOI,Q路混频器的本振信号差分输入端MLOP和MLON连接Q路本振信号MLOQ。复数滤波器的I路差分输入端FIIP和FIIN分别连接I路混频器的输出端MOP和MON,Q路差分输入端FIQP和FIQN分别连接Q路混频器的输出端MOP和MON,增益控制端GSW连接增益控制字gsw,I路差分输出端FOIP和FOIN连接到接收前端的I路输出端IOUTP和IOUTN,Q路差分输出端FOQP和FOQN连接到接收前端的Q路输出端QOUTP和QOUTN。时间常数校正电路CAL的输出端CSW连接到复数滤波器的电容阵列控制输入端CSW。

具有多种增益模式的、能自动调谐的射频接收前端的工作原理是,电流模的低噪声放大器、无源混频器和有源RC复数滤波器配合使用,具有低噪声、高线性度的优点;低噪声放大器LNA在输入端的共栅放大管的栅极和漏极同时实现增益控制,同时通过与电阻负载串联的开关来控制负载大小,进而对增益进行校正,复数滤波器也能进行增益控制,这使得整个接收前端具有大的动态范围;复数滤波器的电容采用阵列结构,能通过校正电路进行自动校正,电容阵列的开关能确保完全关闭,提高了总电容值的精度;时间常数较正电路对有源RC复数滤波器的RC时间常数进行自动校正,能保证接收前端的性能,采用二分法搜索,加快了校正速度。

本发明实施例的低噪声放大器的电路图如图2所示,PMOS管Mp1、Mp2、Mp3和Mp4的源极都接到电源电压VDD上,Mp1和Mp2的栅极连接增益控制字lsw1,Mp3和Mp4的栅极连接增益控制字lsw2。NMOS管Mn1和Mn2的栅极分别连接到偏置电压Vb1和Vb2上。NMOS管Mn3的漏极与NMOS管Mn4的漏极相连,Mn3的源极与NMOS管Mn5的漏极相连,Mn3、Mn4和Mn5的栅极相连后连接到控制字lsw3上,Mn4与Mn5的源极接地。NMOS管Mn6的漏极连接到Mn1的漏极,Mn6的源极连接到Mn2的漏极,Mn6的栅极连接到增益控制字lsw4。NMOS管Mn7和Mn8的栅极相连后连接到偏置电压Vb3,Mn7的源极连接到Mn1的漏极,Mn8的源极连接到Mn2的漏极。电感L1连接低噪声放大器的同相输入端LIP和Mn4的漏极,电感L2连接低噪声放大器的反相输入端LIN和Mn5的漏极,电感L3连接Mn1的源极和地,电感L4连接Mn2的源极和地。电容C1连接Mn1的栅极和Mn4的漏极,电容C2连接Mn2的栅极和Mn5的漏极。电阻R1连接Mp1的漏极和Mn7的漏极,电阻R2连接Mp2的漏极和Mn8的漏极,电阻R3连接Mp3的漏极和Mn7的漏极,电阻R4连接Mp4的漏极和Mn8的漏极。

本发明实例的低噪声放大器的输入端Mn3、Mn4和Mn5构成的开关来实现增益控制,本例中是一个开关,实际上可以有任意多个类似的开关在输入端控制增益。当增益控制字lsw3为高电平时,NMOS管Mn4和Mn5导通,使得Mn4和Mn5相当于两个小电阻,并且Mn4和Mn5的漏极电势降低使得Mn3也导通,Mn3也相当于一个阻值很小的电阻。这样输入的差分信号一方面通过Mn4和Mn5旁路到地衰减,另一方面通过Mn3衰减,以实现增益的降低,进而增强接收机的抗大信号饱和能力。通过更多的开关可以做出更大的衰减,进而进一步增大增益调节的范围。当增益控制字lsw3为低电平时,Mn3、Mn4和Mn5都不导通,并且Mn3、Mn4和Mn5的尺寸可以设计的很小,寄生电容小,这样此时输入信号不被衰减。中间部分通过Mn6控制增益,当控制字lsw4为高时,Mn6导通,增益下降;当控制字lsw4为低时,Mn6截止,增益提高。输出端通过PMOS开关管Mp1、Mp2、Mp3和Mp4来校准由于工艺偏差而引起的增益误差,通过控制字lsw1和lsw2开改变输出负载,进而改变增益。低噪声放大器具有全差分的结构,降低了共模噪声。采用电阻做负载,与电感做负载的低噪声放大器相比,减小了面积。

本发明实施例的混频器的电路图如图3所示,运算放大器OTA的差分输出OP和ON连接到混频器的差分输出端MON和MOP,NMOS管M1和M3的漏极相连后连接到OTA的同相输入端,NMOS管M2和M4的漏极相连后连接到OTA的反相输入端,M1和M2的源极相连,M3和M4的源极相连,M1和M4的栅极相连,M2和M3的栅极相连。电容C1连接OTA的同相输入端和反相输出端,电容C2连接OTA的反相输入端和同相输出端,电容C3连接OTA的同相输入端和地,电容C4连接OTA的反相输入端和地,电容C5连接M1的源极和混频器的同相输入端MIP,电容C6连接M3的源极和混频器的反相输入端MIN,电容C7连接M1的栅极和混频器的本振信号同相输入端MLOP,电容C8连接M3的栅极和混频器的本振信号反相输入端MLON。电阻R1连接OTA的同相输入端和反相输出端,电阻R2连接OTA的反相输入端和同相输出端,电阻R3连接OTA的同相输入端和能隙基准源,电阻R4连接OTA的反相输入端和能隙基准源,电阻R5连接M1的栅极与能隙基准源,电阻R6连接M1的源极与能隙基准源,电阻R7连接M3的栅极与能隙基准源,电阻R8连接M3的源极与能隙基准源。

本发明实施例的混频器为无源电流模混频器,具有高线性度、低噪声、低功耗的特点。通过能隙基准源来设置偏置电压,使得开关管M1、M2、M3和M4处于即将导通的状态,本振信号通过电容C7和C8交流耦合到开关管上,这样使得M1、M2、M3和M4中没有直流电流,降低了闪烁噪声。本发明实施例的混频器自带低通滤波器,能够兼做通道滤波器的作用。高增益、高带宽的运算放大器OTA保证了虚地点上信号幅度很小,同时在虚地点处加入一个电容,引入一个多余的极点,进一步压制了信号幅度,而且不改变输出信号的带宽,与电流模的低噪声放大器配合使用,使得整个射频接收前端具有高线性度。

本发明实施例的复数滤波器的框图如图4所示,第一级复数滤波器单元CF1的I路差分输入端Iin+和Iin-连接到整个复数滤波器的I路差分输入端FIIP和FIIN,第一级复数滤波器单元CF1的Q路差分输入端Qin+和Qin-连接到整个复数滤波器的Q路差分输入端FIQP和FIQN,第二级复数滤波器单元CF2的I路差分输入端Iin+和Iin-连接到CF1的I路差分输出端Iout+和Iout-,第二级复数滤波器单元CF2的Q路差分输入端Qin+和Qin-连接到CF1的Q路差分输出端Qout+和Qout-,第三级复数滤波器单元CF3的I路差分输入端Iin+和Iin-连接到CF2的I路差分输出端Iout+和Iout-,第三级复数滤波器单元CF3的Q路差分输入端Qin+和Qin-连接到CF2的Q路差分输出端Qout+和Qout-,第四级复数滤波器单元CF4的I路差分输入端Iin+和Iin-连接到CF3的I路差分输出端Iout+和Iout-,第四级复数滤波器单元CF4的Q路差分输入端Qin+和Qin-连接到CF3的Q路差分输出端Qout+和Qout-,第四级复数滤波器单元CF4的I路差分输出端Iout+和Iout-连接到整个复数滤波器的I路差分输出端FOIP和FOIN,第四级复数滤波器单元CF4的Q路差分输出端Qout+和Qout-连接到整个复数滤波器的差分输出端FOQP和FOQN。复数滤波器每一级单元的增益控制字输入端gsw连接到整个复数滤波器的增益控制字输入端GSW。各级的电容阵列控制字输入端fsw相连后连接到整个复数滤波器的电容阵列控制字输入端CSW。

本实施实例的复数滤波器采用有源RC的结构,具有高动态范围、高线性度的特点。在由低噪声放大器、混频器、复数滤波器组成的整个射频接收前端中,对射频接收前端的线性度影响最严重的是复数滤波器,所以采用高线性度的有源RC结构提高了整个接收前端的线性度。本发明中的复数滤波器以四级为例,实际上可以有任意多级级联。

本实施实例的复数滤波器单元电路如图5所示,运算放大器OPA1的差分输出端连接到整个复数滤波器单元的I路差分输出端,运算放大器OPA2的差分输出端连接到整个复数滤波器单元的Q路输出端。电容阵列单元Ca1连接运算放大器OPA1的同相输入端和反相输出端,电容阵列单元Ca2连接运算放大器OPA1的反相输入端和同相输出端,电容阵列单元Ca3连接运算放大器OPA2的同相输入端和反相输出端,电容阵列单元Ca4连接运算放大器OPA2的反相输入端和同相输出端,Ca1、Ca2、Ca3和Ca4的电容控制字输入端SW连接在一起后连接到电容控制字fsw。NMOS管M1的漏极连接到OPA1的同相输入端,NMOS管M2的漏极连接到OPA1的反相输入端,NMOS管M3的漏极连接到OPA2的同相输入端,NMOS管M4的漏极连接到OPA2的反相输入端,M1、M2、M3和M4的栅极相连后连接到增益控制字输入端gsw。电阻R1连接OPA1的同相输入端和反相输出端,电阻R2连接OPA1的反相输入端和同相输出端,电阻R3连接OPA1的反相输入端和OPA2的反相输出端,电阻R4连接OPA1的同相输入端和OPA2的同相输出端,电阻R5连接OPA1的反相输出端和OPA2的同相输入端,电阻R6连接OPA1的同相输出端和OPA2的反相输入端,电阻R7连接OPA2的同相输入端和反相输出端,电阻R8连接OPA2的反相输入端和同相输出端。电阻R9连接NMOS管M1的源极和漏极,电阻R10连接NMOS管M2的源极和漏极,电阻R11连接NMOS管M3的源极和漏极,电阻R12连接NMOS管M4的源极和漏极。电阻R13连接M1的源极和复数滤波器单元的I路反相输入端Iin-,电阻R14连接M2的源极和复数滤波器单元的I路同相输入端Iin+,电阻R15连接M3的源极和复数滤波器单元的Q路反相输入端Qin-,电阻R16连接M4的源极和复数滤波器单元的Q路同相输入端Qin+。

本实施实例的复数滤波器单元通过NMOS开关管M1、M2、M3和M4控制电阻实现增益控制,具有宽的动态范围。当增益控制字输入gsw为高电平时,电阻R9、R10、R11和R12被短路掉,复数滤波器单元处于高增益模式;当增益控制字输入gsw为低电平时,M1、M2、M3和M4关闭,复数滤波器单元处于低增益模式。跨接在OPA输入和输出端的电阻固定,电容为可控阵列,通过调节电容阵列实现时间常数的调谐。

本实施实例的时间常数校正电路如图6所示,运算放大器OTA1的同相输入端、运算放大器OTA2的同相输入端、运算放大器OTA3的同相输入端和运算放大器OTA4的反相输入端都连接到能隙基准源上。运算放大器OTA3和OTA4用作比较器,输出连接到数字电路。NMOS管M1的栅极连接到OTA1的输出端,M1的源极连接到OTA1的反相输入端,M1的漏极连接到OTA2的反相输入端。NMOS管M2的栅极连接到数字电路,M2的源极连接到OTA2的反相输入端,M2的漏极连接到OTA2的输出端。电容阵列Ca连接OTA2的反相输入端和输出端,Ca的控制字输入端SW连接到数字电路,同时连接到时间常数校正电路的输出端CSW。电阻阵列Ra连接NMOS管M1的源极和地。

本实施实例的时间常数校正电路的工作原理是,通过运算放大器OTA1和能隙基准源,给OTA1的反相输入端一个固定的电压,这在电阻阵列Ra中产生一个电流,数字电路产生时钟控制开关管M2,初始状态M2关断,电流对电容阵列Ca充电,充电的结果决定OTA2的输出电压值,这个电压值与OTA3的同相输入端电压和OTA4的反相输入端电压作比较,比较的结果通过OTA3和OTA4输出到数字电路,数字电路根据比较的结果调整电容阵列Ca的值,同时将调整后的控制字送到输出端。当复数滤波器中的电阻或电容因为工艺、温度发生偏差时,校正电路中的电阻阵列Ra和电容阵列Ca发生相同百分比的偏差,充电后OTA2的输出电压发生变化,OTA3和OTA4的输出结果也相应的发生变化,数字电路将改变Ca的电容值。充电周期地进行,每次充电结束后数字电路将开关M2打开,使Ca放电,然后下一周期再进行下一次充电。如此往复的充电,不断地调整电容阵列,直到OTA2的输出电压在OTA3的同相输入端电压和OTA4的反相输入端电压之间时,校正停止,此时输出的控制字CSW用来控制复数滤波器中的电容阵列,实现校正复数滤波器时间常数的目的。

本发明实施实例的电容阵列单元如图7所示,NMOS管M1、M2、M3和M4的源极连接后连接到电容阵列单元的输入端L,M1的栅极连接电容阵列控制字CSW的第一位CSW1,M2的栅极连接电容阵列控制字CSW的第二位CSW2,M3的栅极连接电容阵列控制字CSW的第三位CSW3,M4的栅极连接电容阵列控制字CSW的第四位CSW4。NMOS管M5的源极和M1的漏极相连,NMOS管M6的源极和M2的漏极相连,NMOS管M7的源极和M3的漏极相连,NMOS管M8的源极和M4的漏极相连,M5、M6、M7、M8的漏极相连。电容C1连接M1的漏极和电容阵列的输入端R,电容C2连接M2的漏极和电容阵列的输入端R,电容C3连接M3的漏极和电容阵列的输入端R,电容C4连接M4的漏极和电容阵列的输入端R。反相器INV1的输入端连接到M1的栅极,反相器INV1的输出端连接到M5的栅极,反相器INV2的输入端连接到M2的栅极,反相器INV2的输出端连接到M6的栅极,反相器INV3的输入端连接到M3的栅极,反相器INV3的输出端连接到M7的栅极,反相器INV4的输入端连接到M4的栅极,反相器INV4的输出端连接到M8的栅极。电阻R1连接电源电压VDD和NMOS管M5的漏极,电阻R2连接NMOS管M5的漏极和地。本发明的电容阵列单元中,以四个电容为例,实际上可以有任意多个电容。

本实施实例的电容阵列单元的工作原理是,输入端L和R的共模电压设置在供电电压的1/2,当电容阵列控制字CSW1、CSW2、CSW3和CSW4为等于供电电压的高电平时,M1、M2、M3和M4导通,而M5、M6、M7和M8关闭,这时电容C1、C2、C3和C4全部生效;当电容阵列控制字CSW1、CSW2、CSW3和CSW4为低电平时,M5、M6、M7和M8导通,这将M1、M2、M3和M4的漏极电压钳位在供电电压的1/2,确保了M1、M2、M3和M4能完全截止,此时C1、C2、C3和C4全部无效。通过上述方法改变电容阵列控制字来实现电容阵列的调节。本发明的优点是通过辅助开关M5、M6、M7和M8的电压钳位,使得开关M1、M2、M3和M4均能有效的关闭,保证了总电容值的准确性。

本实施实例的时间常数校正电路能通过一套电路校正任何多级有源RC滤波器中的所有电容阵列,具有低成本、低功耗的优点。同时,数字电路在调整电容阵列控制字时采用二分法搜索,提高了校正速度。

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,本发明的射频接收前端各部件所包含的NMOS管、PMOS管、电容、电阻的个数不限于上述权利要求所限定的数量,可以根据实际情况选择其个数,在不脱离本发明技术原理的前提下,还可以做出若干改进和变型,这些改进和变型也应视为本发明的保护范围。

具有多种增益模式、能自动调谐的射频接收前端专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0