专利摘要

本发明涉及基于开口孔共振耦合效应的等离激元全光逻辑器件,利用三个开口孔共振器在横向和纵向两个维度调整以改变耦合强度来丰富各端口的输出状态,其具有小尺寸、低功耗的特点,属于光电子集成技术领域。

权利要求

1.一种基于开口孔共振耦合效应的等离激元全光逻辑器件,由多个沿纵向错位排布的开口孔构成干涉通道构成,开口孔的中心不在沿纵向的直线上,可以通过横向和纵向两个维度对开口孔之间的耦合距离作出调整,其中,单个开口孔为在尺度小于微米量级的立方体形的贵金属颗粒上刻蚀出的一空气狭槽和空气孔结构,空气狭槽穿过空气孔的中心。

2.如权利要求1所述的等离激元全光逻辑器件,其特征在于,所述贵金属材料为金、银、铜或铝。

3.如权利要求1所述的等离激元全光逻辑器件,其特征在于,所述立方体为正方体、长方体、多面体或圆柱体。

4.如权利要求1所述的等离激元全光逻辑器件,其特征在于,所述开口孔为单条空气狭槽或对称性采用多条空气狭槽。

5.如权利要求1所述的等离激元全光逻辑器件,其特征在于,所述多个开口孔为两个、三个开口孔或更多个。

6.如权利要求1所述的等离激元全光逻辑器件,其特征在于,所述干涉通道包括空气狭槽和空气孔构成的传输通道和立方体颗粒外侧面激发等离激元构成的传输通道。

7.利用权利要求1所述的等离激元全光逻辑器件建立各端口的共振输出强度与输入端输入状态的逻辑关系的方法,其特征在于,定义输入端口、触发端口有输入时为状态“1”,无输入时为状态“0”,输出端口监测各个输入状态触发下实际测得的功率。

8.利用权利要求1所述的等离激元全光逻辑器件建立满足一定的功率阈值要求下实现逻辑功能的方法,其特征在于,根据输出端口监测到的功率,定义输出状态“0”和“1”的功率范围,建立输入状态与输出状态之间的逻辑关系。

说明书

技术领域

本发明涉及光电子集成技术领域,特别涉及一种基于开口孔共振器的等离激元全光逻辑器件。

背景技术

当今微处理器的工艺水平,主要基于超快速纳米级的晶体管,尺寸在大约50纳米。目前快速晶体管的常规生产已不成问题,主要的问题在于如何将数字信息传送到微处理器的另一端,大约几厘米之遥。随着电路中集成晶体管的数目指数增加,采用铜导线连接它们,已经不能满足要求。连线中信息延迟的加剧,也已成为阻碍数字电路速度进一步提高的一个瓶颈。微处理器的提速,近一两年来,其年度增长率已明显地减缓。

光子互连元件能够携带数据的容量是电子互连器的100倍,然而,光纤光缆的尺寸是电子元件的100倍,由于尺度上不兼容,使两者难于集成于同一回路中。一个理想的解决途径是采用等离激元元件。

全光逻辑门在全光数字信号处理如光寻址、开关、奇偶校验、数字编码和加密,包括高速光网络通信等方面有潜在的应用。实现光逻辑门是获得光信号处理和光计算系统的基本要求。至今,逻辑门的研究工作主要是基于传统技术如光纤、波导干涉仪、半导体光放大器和微共振器。然而,传统技术有其内在的缺点,如基于光纤的逻辑门很难实现芯片上集成,基于介质波导干涉仪的逻辑门通常需要复杂的结构,减小尺寸也是一个挑战,半导体光放大器和微共振器不可避免地受自发辐射噪声的限制。光子晶体可用于集成芯片实现超快开关,显著减小尺寸和降低功耗。基于光子晶体平台的不同光逻辑门被报道了很多。但光子晶体需要周期性的结构,元件的尺寸仍然在数微米的量级,不利于大规模的集成,更不利于与成熟的电子线路的连接。而等离激元器件可以同时获得电子器件的集成度和光子器件的速度和信息量。基于表面等离激元的纳米光子学的发展,纳米技术与光子技术结合,使人们对等离激元结构的研究产生了浓厚的兴趣,如等离激元沟道波导,纳米粒子链,纳米柱等等,通过光子与电子相互作用在金属表面振荡来导光,使纳米量级光元件得到快速发展。然而,对这些波导来说,对光的限制程度和传输损耗之间需要平衡处理。最近,Margheri等人采用波浪形薄金属膜和具有三阶非线性光学效应的介质形成的多层结构实现了全光开关。Geum-Yoon Oh等人则报道了一种基于有源等离激元的新型全光逻辑门,通过外部光注入来调控有源层的折射系数。国内中科院物理所魏红等研制了基于金属纳米线的表面等离激元通用逻辑门,北京大学龚旗煌研究组则基于具有长程传输和亚波长强光场局域特性的新型表面等离激元波导结构,实现了“0”和“1”强度对比达24dB的超低功率、小型化的微纳全光逻辑门器件。南京大学祝世宁研究组提出了利用纳米三明治、开口环等结构构成磁等离激元模式传输的链路波导,但他们未将磁等离激元的结构应用于全光逻辑器件的研究。

发明内容

本发明设计了一种基于开口孔共振耦合效应的等离激元全光逻辑器件,需要解决耦合开口孔沿横向和纵向的位移对空气孔侧壁感应电流并联分流的影响问题,以及立方体颗粒外侧壁磁致感应电流引起等离激元波的干涉而导致的不同端口共振输出的强弱与波长的对应关系问题。需要对结构的各个参数优化,以使逻辑门的工作状态达到最优,同时又减少辐射损耗和欧姆损耗。

本发明基于开口孔磁等离激元共振耦合效应,利用三个开口孔共振器在横向和纵向两个维度调整以改变耦合强度,构建小尺寸、低功耗的等离激元全光逻辑器件。

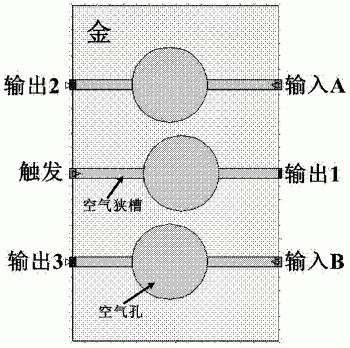

这种等离激元全光逻辑器件为在立方体形的贵金属颗粒上刻蚀出空气狭槽和空气孔构成开口孔结构(狭槽穿过空气孔的中心),由三个这样的开口孔沿纵向错位排布而构成,如图1所示。

优选地,器件所用材料可以是金,也可以是其他贵金属材料,如银、铜、铝等。立方体颗粒形状可以是正方体,也可以是长方体、多面体、圆柱体等。开口孔不限于单条空气狭槽,也可以根据对称性采用多条空气狭槽。

上述方案中,通过横向和纵向两个维度对开口孔之间的耦合距离作出调整,开口孔的中心不在沿纵向的直线上,使得空气孔两边的空气狭槽长度不等。逻辑器件的开口孔结构可以是两个、三个开口孔,也可以由更多个开口孔构成。

上述方案中,可以定义两个输入端、一个触发端和一个输出端构成逻辑与门,但这种结构不限于逻辑与,设置其他的输出端口,定义监测功率与输出状态关系,也可实现其他的逻辑功能。

本发明具有以下有益效果:

1、该逻辑器件利用开口孔共振结构的磁等离激元模式,相比一般的表面等离激元工作模式来说,具有低的辐射损耗和长的传输距离等优势。

2、不需引入任何非线性材料,因而大大降低了入射光功率,同时也不存在探测信号和输入信号波长不一样的情况,可完全实现同一波长的门控操作,即触发端和信号输入端的光波长相同。

3、器件结构能够在横向和纵向两个维度调整,以改变开口孔之间的耦合强度,使各端口的输出情况更加丰富,不同的输出端口可能实现不同的逻辑功能。

4、器件结构基于立方体金属颗粒,总体尺寸处于亚微米量级,远小于一般的表面等离激元逻辑器件的尺寸,从而实现无高功率阈值要求、小尺寸的全光逻辑器件。

附图说明

为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明,其中:

图1是器件结构示意图;

图2(a)是三维单开口孔结构示意图,(b)是单开口孔结构俯视图,(c)、(d)是单开口孔结构中的电场、磁场强度分布,(e)是磁感应电荷及电流分布示意图;

图3是四种状态下输出端口1的共振输出功率,插图为等离激元逻辑与门的俯视结构示意图;

图4是四种状态下的能流密度分布,(a)A“0”B“0”,(b)A“0”B“1”,(c)A“1”B“0”,(d)A“1”B“1”;

具体实施方式

基于开口孔共振耦合效应的等离激元全光逻辑器件,由三个沿纵向错位排布的开口孔构成,如图1所示。利用单个开口孔的磁等离激元共振效应以及多开口孔排布的对称性破缺引起的磁致电荷的非均匀分布共同作用下等离激元波的干涉,建立各端口的共振输出强度与输入端输入状态的逻辑关系,在满足一定的功率阈值要求下,实现如逻辑与门的功能。

所述的单个开口孔,为在尺度小于微米量级的立方体形的贵金属颗粒上刻蚀出一空气狭槽和空气孔结构,狭槽穿过空气孔的中心。所用材料不限于金,也可用其他贵金属材料如银、铜、铝等。立方体不限于正方体,也可用长方体、多面体、圆柱体等。开口孔不限于单条空气狭槽,也可以根据对称性采用多条空气狭槽。

所述的等离激元全光逻辑器件,利用了单个开口孔的磁等离激元共振效应,磁等离激元的传输具有低的辐射损耗和长的传输距离等优势。在不限于单条空气狭槽的情况下,磁等离激元可在开口孔中形成多模干涉的效果。

所述的多开口孔排布的对称性破缺引起的磁致电荷的非均匀分布,可以通过横向和纵向两个维度对开口孔之间的耦合距离作出调整,开口孔的中心不在沿纵向的直线上,从而导致空气孔两边的空气狭槽长度不等,这种结构的对称性破缺导致磁致电荷的非均匀分布,使得电磁场的非对称局域分布,给每个通道和输出端口的能流带来差异。多开口孔结构不限于两个、三个开口孔,也可以有更多个。

所述的等离激元波的干涉,其干涉通道既包括空气狭槽和空气孔构成的传输通道,又包括立方体颗粒外侧面激发出的电荷构成的传输通道,在特定的波长满足完全相干条件,使得特定输出端口测得共振传输谱出现明显的Fano共振线型,如两开口孔结构。

所述的各端口的共振输出强度与输入端输入状态的逻辑关系,定义输入端口、触发端口有输入时为状态“1”,无输入时为状态“0”,输出端口监测各个输入状态在触发时实际测到的功率。

所述的满足一定的功率阈值要求下实现逻辑功能,根据输出端口监测到的功率,定义输出状态“0”和“1”的功率范围,即功率阈值,建立输入状态与输出状态之间的逻辑关系。

所述的基于开口孔共振耦合效应的等离激元全光逻辑器件,是首次将磁等离激元结构经过特殊排布后形成的无高功率阈值要求、小尺寸的全光逻辑与门。但这种结构不限于逻辑与,设置其他的输出端口,定义监测功率与输出状态关系,也可实现其他的逻辑功能。

参照图1,展示了器件的结构示意图。

参照图2,展示了三维单开口孔结构及其俯视图,以及单开口孔结构中的电场、磁场强度分布,磁感应电荷及电流分布。

参照图3,展示了四种状态下输出端口1的共振输出功率。

参照表1,展示了等离激元逻辑门的真值表。

参照图4,展示了四种状态下的能流密度分布。

表1等离激元逻辑门的真值表

实施例1

图2(a)(b)所示为单开口结构,由在立方体形的金颗粒上刻蚀出一空气狭槽和空气孔构成,狭槽穿过空气孔的中心。空气孔半径r=58nm,空气孔两侧的空气狭槽长度l=100nm,槽宽w=15nm,立方体厚度H=105nm。图2(c)为电场强度分布图,图2(d)为磁场强度分布图。很显然,电场主要局域在空气狭槽中,而磁场主要局域在空气孔中。这里空气狭槽的尺寸主要允许磁等离激元基模存在。从色阶图看出,结构中电场强度的最大值明显大于磁场,但是稍微偏离结构的地方,磁场的强度要高于电场,这充分说明了结构对电场的高度局域。

与之类似的结构,南京大学的刘辉曾经研究过,他们基于开口孔结构的一维单原子链和双原子链,分别研究了磁等离激元的传输。而我们这里采用的开口孔结构,是为了共振传输磁等离激元并能对信号实现逻辑操控。

我们进而分析这种共振模式的形成机理。在外部输入信号磁分量的激励下,空气孔侧壁形成磁感应电荷传输通道,空气狭槽也会激发出相应的感应电荷,这样在整个开口孔结构的上下内侧壁就形成磁感应电流的回路(图2(e)所示),稳定状态下从而形成特定的磁等离激元模式的电磁场局域。这时,在信号输出端测到的信息可以认为是开口孔结构振荡腔的泄漏。

基于三开口孔耦合的等离激元逻辑与门如图3所示,中间空气孔中心相对纵向的中轴线右偏9nm,上下空气孔中心相对纵向的中轴线左偏9nm,上下空气孔边缘距离中间空气孔边缘20nm。保持r=58nm,l=100nm,w=15nm,H=105nm。左边三个端口由上而下分别为输出端口2、触发端口、输出端口3,右边三个端口由上而下分别为输入端口A、输出端口1和输入端口B。触发端口保持始终有输入,在输入端口A和B不同的输入状态下,考察输出端口1的输出情况。表1所示真值表中的0表式该端口没有输入,1表示有输入,功率为实际监测到的值。图3为模拟计算得到处于不同工作状态下的光谱图。定义共振波长1.92μm为工作波长。当输入端A和B都没有输入时,仅触发端有输入,输出端1测到的功率为143。当仅B端口有输入时,测到的功率为496,而当仅A端口有输入时,测到的功率为501,这两种情况几乎没有差别。当A端口和B端口都有输入时,测到的功率为1631。定义测到的功率小于或等于501为输出0的状态,功率大于或等于1631为输出1的状态,这样确定出的开关比约为3.3,表1列出了四种状态的真值表。图4还给出了对应的能流分布图,与真值表的四种状态能够很好对应,体现出了全光逻辑器件的功能。

全光逻辑器件可分成主要两类:一是基于线性光学效应,及所谓的干涉型逻辑器件,二是基于非线性光学效应,主要是因为泵浦光引起介质的折射率变化。由于干涉型逻辑器件基于两个输入信号的相对光学相位实现,因而内在的稳定性是一大挑战,这种挑战可以通过减小器件尺寸和单片集成来减轻,同时需要更精确的设计和更高标准的制造技术来完成。干涉型逻辑器件由于没有非线性效应的参与,不需额外的高功率的泵浦光,因而也称为“零能量”逻辑,本方案所涉及结构即属于这种类型器件。

以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

基于开口孔共振耦合效应的等离激元全光逻辑器件专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0