专利摘要

本发明公开了一种具有启动停止控制位的插值FIR滤波实现方法,在一个数据包处理完毕后使寄存器不再移位,所有的移位寄存器里的数据都保持在数据包的最后一个数据输入时的状态;下一个数据包到来时,完整的与上一个数据包对接,新输入的数据与前N‑1个数据的相关性没被破坏,保证了大量连续数据的无间隔处理,其中N为移位寄存器个数。本发明具有原理简单、易实现、能够令各移位寄存器在各个包间隙数据保持不变、保证数据连续及相关性等优点。

权利要求

1.一种具有启动停止控制位的插值FIR滤波实现方法,其特征在于,在一个数据包处理完毕后使寄存器不再移位,所有的移位寄存器里的数据都保持在数据包的最后一个数据输入时的状态;下一个数据包到来时,完整的与上一个数据包对接,新输入的数据与前N-1个数据的相关性没被破坏,保证了大量连续数据的无间隔处理,其中N为移位寄存器个数;在插值FIR滤波器中移位寄存器间设置多路选择器,选择信号是输入的控制信号control;所述控制信号control为高时寄存器正常移位到下一级,否则,移位到本寄存器输入端,保持移位寄存器中数据的不变。

2.根据权利要求1所述的具有启动停止控制位的插值FIR滤波实现方法,其特征在于,连接插值FIR滤波器与微控制器的AXI总线针对外设分配专用的输入输出缓存区,这些输入输出缓存区向下被接口电路当做RAM或寄存器使用,向上被C程序读写;FIR滤波器的数据data从处理器经AXI数据总线发送到FIR滤波器指定缓存区RAM,只有一次性要处理的数据全部搬运到FIR滤波器缓存区RAM之后,滤波器才能开始处理。

3.根据权利要求2所述的具有启动停止控制位的插值FIR滤波实现方法,其特征在于,在缓存区RAM中某一不会被待处理数据覆盖的一个存储单元,把该存储单元定义成标志位Flag,这个标志位地址能够被C程序访问,并且将这个标志位Flag作为寄存器变量在接口电路中直接连接到FIR滤波器的启停位control;标志位Flag不能靠C程序手动置0,因为信号从C程序经过数据总线传输到标志位Flag后的时间不确定,而控制位control需要在处理完数据后立即停止,否则多采样无效数据;设置一个计数counter,在计数满一个包数据数据的时候对标志位Flag清0。

说明书

技术领域

本发明主要涉及到数字信号处理技术领域,特指一种具有启动停止控制位的插值FIR滤波实现方法。

背景技术

在数字信号处理领域,数字滤波器是必不可少的基本器件,其中FIR滤波器又是最常用的数字滤波器结构,也就是有限长单位脉冲响应数字滤波器,FIR输出对应于输入时间序列x(n)的关系,由一种有限卷积数量形式给出,公式为:

最基本的FIR滤波器结构是直接型结构,直接型结构的FIR滤波器结构如图1,主要包括移位寄存器和乘法器加法器。关于FIR滤波器的结构已经有很多种改进,如串行FIR滤波器、并行FIR滤波器、半并行FIR滤波器、分布式FIR滤波器等。

基于移位寄存器的串行FIR滤波器的设计思想是输入数据周期性的动态流动是以自身的流动而非通过地址的改变实现的。如图2所示,每完成一次滤波运算,输入数据沿数据窗推进一格,即总有一格新的数据进入数据窗并占据数据窗的第一个位置,数据窗内的原有数据整体向前推移一个系数位,且总有一格数据一处数据窗。输入数据的这种流动特性可采用移位寄存器实现。基于移位寄存器的串行FIR滤波器结构如图3所示。

在某些场合,FIR滤波器的采样频率很高,实时性很强,这就要求其具有很高的处理速度和数据吞吐率。全并行结构就满足了这一要求。它使得采样频率与系统处理速度相当。其思想是将一次滤波运算内的乘法同时执行,最终达到“以资源换速度”的目的。采用加法树的直接型结构FIR滤波器使用流水线计数进行处理以缩短关键路径,得到如图4所示的基于直接型结构的4抽头采用加法树的全并行FIR滤波器硬件结构。这种结构是将一次滤波运算的所有乘法同时执行。

插值FIR滤波器是FIR滤波器的一种,插值意味着提高采样频率,故也可称之为上采样。假定原始序列为x(n),采样频率为fx,插值因子为L,则插值过程可描述为在原始序列每相邻采样点钟插入L-1个0构成新序列。一般的插值滤波器结构由插值器和滤波器组成。插值后相邻的两个采样点之间引入L-1个零,显然对这L-1个零的运算时没有必要的。所以通常插值的FIR滤波器并不需要耗费这么多乘法器资源,而可以采用多相结构,将一个大的插值滤波器分解成若干个子滤波器。分时复用延时单元和乘法器后,可以得到改进的结构。以5倍插值26阶插值FIR滤波器为例,5倍插值的滤波器,每一个有效数据间隔内插4个0,也就是只有x0,x5,x10……是有效数据,其余为0。每个输出与输入序列的关系:

Y0=x0*h0;

Y1=x1*h0+x0*h1=x0*h1;

Y2=x2*h0+x1*h1+x0*h2=x0*h2;

Y3=x3*h0+x2*h1+x1*h2+x0*h3=x0*h3;

Y4=x4*h0+x3*h1+x2*h2+x1*h3+x0*h4=x0*h4;

Y5=x5*h0+x4*h1+x3*h2+x2*h3+x1*h4+x0*h5=x5*h0+x0*h5;

Y6=……=x5*h1+x0*h6;

Y7=……=x5*h2+x0*h7;

Y8=……=x5*h3+x0*h8;

Y9=……=x5*h4+x0*h9;

Y10=……=x10*h0+x5*h5+x0*h10;

……

Y25=x25*h0+x20*h5+x15*h10+x10*h15+x5*h20+x0*h25;

Y26=x25*h1+x20*h6+x15*h11+x10*h16+x5*h21;

Y27=x25*h2+x20*h7+x15*h12+x10*h17+x5*h22;

Y28=x25*h3+x20*h8+x15*h13+x10*h18+x5*h23;

Y29=x25*h4+x20*h9+x15*h14+x10*h19+x5*h24;

Y30=x26*h0+x25*h5+x20*h10+x15*h15+x10*h20+x5*h25;

……

观察上式规律,每个输入最多有6个乘法相加,每个有效输入(x0,x5,x10……)分别按h0,h1,h2,h3……的顺序依次与系数相乘,每相乘5个系数,就有新的有效数据输入。按照此规律,可以将系数5个一起进行分组,进行循环移位,系数移位的速度是移位寄存器移位速度的5倍,保证每移位一次都与5个系数分别相乘,输出5个结果。这样26阶的插值FIR滤波器只需要6个移位寄存器和6个乘法器。节省了资源,而且每时钟周期都可以输出一结果,结构如图5。

网络通信中的数据通常是以多帧的格式传输的,要传输的数据被打包,一份一份的在从主机和从机之间通信。从PC机经网线传输来的数据进行无线传输时,数据通过无线信道环境之前必须要经过FIR插值滤波器才能保证数据在接收端能被正确解析出。FIR滤波器是串行输入数据,数据要源源不断的输入,由于进行卷积运算,对于N阶的FIR滤波器,每一个新进入移位寄存器里的数据都与之前N-1个已经进入移位寄存器里的数据序列相关。然而各个数据包之间有时间间隔,如果不采用任何结构,滤波器移位寄存器会被新采样的无效数据填充,导致新数据与旧数据之间的数据相关性被破坏,输出错误的数据。

发明内容

本发明要解决的技术问题就在于:针对现有技术存在的技术问题,本发明提供一种原理简单、易实现、能够令各移位寄存器在各个包间隙数据保持不变、保证数据连续及相关性的具有启动停止控制位的插值FIR滤波实现方法。

为解决上述技术问题,本发明采用以下技术方案:

一种具有启动停止控制位的插值FIR滤波实现方法,在一个数据包处理完毕后使寄存器不再移位,所有的移位寄存器里的数据都保持在数据包的最后一个数据输入时的状态;下一个数据包到来时,完整的与上一个数据包对接,新输入的数据与前N-1个数据的相关性没被破坏,其中N为移位寄存器个数。

作为本发明的进一步改进:在插值FIR滤波器中移位寄存器间设置多路选择器,选择信号是输入的控制信号control;所述控制信号control为高时寄存器正常移位到下一级,否则,移位到本寄存器输入端,保持移位寄存器中数据的不变。

作为本发明的进一步改进:连接插值FIR滤波器与微控制器的中AXI总线针对外设分配专用的输入输出缓存区,这些输入输出缓存区向下被接口电路当做RAM或寄存器使用,向上被C程序读写;FIR滤波器的数据data从处理器经AXI数据总线发送到FIR滤波器指定缓存区RAM,只有一次性要处理的数据全部搬运到FIR滤波器缓存区RAM之后,滤波器才能开始处理。

作为本发明的进一步改进:在缓存区RAM中某一不会被待处理数据覆盖的一个存储单元,把该存储单元定义成标志位Flag,这个标志位地址能够被C程序访问,并且将这个标志位Flag作为寄存器变量在接口电路中直接连接到FIR滤波器的启停位control;标志位Flag不能靠C程序对手动置0,因为信号从C程序经过数据总线传输到标志位Flag后的时间不确定,而控制位control需要在处理完数据后立即停止,否则多采样无效数据;设置一个计数counter,在计数满一个包数据的时候对标志位Flag清0。

与现有技术相比,本发明的优点在于:

本发明的具有启动停止控制位的插值FIR滤波实现方法,原理简单、易实现,为针对类似于多帧数据包格式数据的FIR滤波设计,它针对类似于网络数据的多个数据包之间有时间间隙的特点,设计了各移位寄存器在各个包间隙数据保持不变的结构,从而保证了数据的连续及相关性。进一步,本发明还针对停止启动控制位,设计了在嵌入式系统中相应的接口控制电路,保证了软硬件之间的正确握手。

附图说明

图1是现有直接型FIR滤波器结构示意图。

图2是现有4抽头FIR滤波器数据流动的动态变化示意图。

图3是现有基于移位寄存器的串行FIR滤波器结构示意图。

图4是现有基于直接型结构的4抽头采用加法树的全并行FIR滤波器硬件结构示意图。

图5是现有节省乘法资源的插值FIR滤波器结构示意图。

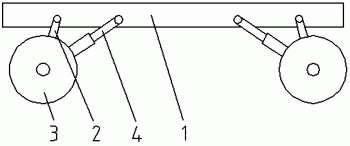

图6是本发明方法在具体应用实例中改变数据通路的移位寄存器结构示意图。

图7是本发明方法在具体应用实例中接口电路与AXI总线和滤波器的连接关系示意图。

图8是本发明方法在具体应用实例中针对多帧数据的有停止启动位的FIR插值滤波器和接口电路结构的示意图。

具体实施方式

以下将结合说明书附图和具体实施例对本发明做进一步详细说明。

本发明的具有启动停止控制位的插值FIR滤波实现方法,是针对网络传输数据的多帧格式特点所进行的插值FIR滤波器设计,该方法的关键就在于:在一个数据包处理完毕后使寄存器不再移位,所有的移位寄存器里的数据都保持在数据包的最后一个数据输入时的状态,这样下一个数据包到来,能够完整的与上一个数据包对接,保证了数据的连续性,新输入的数据与前N-1(N为移位寄存器个数)个数据的相关性没被破坏。

在具体应用实例中,如图6所示,本发明是在移位寄存器间设置多路选择器,选择信号是输入的控制信号control,control为高时寄存器正常移位到下一级,否则,移位到本寄存器输入端,保持移位寄存器中数据的不变。这样,通过把control位作为启动停止位,实现了带启动停止位的FIR插值滤波,构成了FIR插值滤波器,从而可以在两个数据包间隔保持移位寄存器中的数据不变,不丢失与下一个数据包相关的数据。

采用本发明的方法后,基于这样的带有停止启动位的滤波器,就需要外围相应接口电路。为此,AXI总线针对外设分配专用的输入输出缓存区,这些缓存区向下可以被接口电路当做RAM或寄存器使用,向上可以被C程序读写。FIR滤波器数据data从处理器经AXI数据总线发送到FIR滤波器指定缓存区RAM,只有一次性要处理的数据全部搬运到FIR滤波器缓存区RAM之后,滤波器才能开始处理,否则会出现数据顺序错乱。这就需要软件C程序与硬件FIR滤波器之间的握手协议。

在具体应用实例中,本发明进一步在RAM中某一不会被待处理数据覆盖的一个存储单元,比如最后一个存储单单元,把最后一个存储单元定义成标志位Flag,这个标志位地址可以被C程序访问,并且将这个标志位作为寄存器变量在接口电路中直接连接到FIR滤波器的启停位control。标志位Flag不能靠C程序对手动置0,因为信号从C程序经过数据总线传输到标志位后的时间不确定,而控制位control需要在处理完数据后立即停止,否则多采样无效数据。这里添加一个计数counter,在计数满一个包数据数据的时候对标志位清0。接口电路与总线和FIR连接关系如图7所示。

在一次待处理的数据被完整搬运到输入缓存区时,用C程序置标志位Flag为高,从而control也为高,RAM里的数据开始有序送往滤波器的输入端,参与移位寄存器移位。当一个数据包处理完毕,Flag被置为低,从而control也为低,此时移位寄存器不再移位,只是不断刷新自己所存数据,RAM里的数据也无法进入滤波器输入。N阶滤波器的所有的移位寄存器数据保持在最后一个数据输入时的状态。这样,在下一个包写入缓存准备好时,将control置高,数据输入滤波器,可以保证所有数据的连续性,相关性,从而输出正确的数据。

基于本发明的上述实现方法,在具体应用时形成了整体结构,如图8所示,该图8是以26抽头的滤波器为例,以此类推,N抽头的滤波器设计是一样的,均在本发明的保护范围之内。

以上仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,应视为本发明的保护范围。

一种具有启动停止控制位的插值FIR滤波实现方法专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0