专利摘要

本实用新型提供了一种双路信号同传的FM调制发射系统,包括依次串联的模数转换模块、双路信号频分复用模块、FM数字调制模块、数模转换模块、10.7M陶瓷滤波器模块、无源混频器、无源带通滤波器模块、高频功率放大器模块和天线模块;通过将采集到的双路语音信号进行数字处理,将两个子信道合并为新的基带信号,实现频分复用,并经FM数字调制后,通过上变频模块提高载波频率,经过功率放大后通过天线发射出去;FM信号的载波频率和发射功率通过按键输入进行调节。本实用新型结构简单、稳定性好、抗干扰强,实现了双路信号同传的功能。

权利要求

1.一种双路信号同传的FM调制发射系统,其特征在于:包括

分别用于将两路语音电压信号转换为数字信号的模数转换模块1和模数转换模块2,

用于输出FM载波频率和发射功率的控制模块,

用于将FM数字信号转换为FM模拟信号的数模转换模块,

用于滤除包括数字噪声的干扰的滤波器模块1,

用于将中频段的FM模拟信号上变频至高频段的FM模拟信号的上变频模块,

用于滤除包括寄生通道干扰和镜像频率的干扰的滤波器模块2,

用于放大信号功率的放大器模块,

和用于发射信号的天线模块;

模数转换模块1和模数转换模块2的信号输出端分别与控制模块的信号输入端连接,控制模块、数模转换模块、滤波器模块1、上变频模块、滤波器模块2、放大器模块和天线模块依次串联;控制模块的控制端分别与上变频模块和放大器模块的受控端连接,控制模块的时钟输出端分别与模数转换模块1、模数转换模块2和数模转换模块的时钟输入端连接;

模数转换模块1包括依次串联的单端-差分电路和差分-数字电路;单端-差分电路由第一差分放大器U2、反馈电阻、增益设置电阻和终端电阻经过配置放大倍数、配置输入阻抗、采用直流耦合构成;差分-数字电路由第一模数转换器U8经过限制输入带宽和配置时钟后构成;

模数转换模块2包括依次串联的单端-差分电路和差分-数字电路;单端-差分电路由第二差分放大器U2-2、反馈电阻、增益设置电阻和终端电阻经过配置放大倍数、配置输入阻抗、采用直流耦合构成;差分-数字电路由第二模数转换器U8-2经过限制输入带宽和配置时钟后构成;

控制模块包括FPGA芯片U7及其外围元件构成的电路,FPGA芯片U7的内部固化有依次串联的用于对一路语音信号做AM数字调制并与另一路语音信号相加得到基带信号的频分复用模块,和用于通过基带信号控制正弦查找表的相位控制字生成FM数字信号的FM数字调制模块;

数模转换模块包括依次串联的数字-差分电路和差分-单端电路,数字-差分电路包括数模转换器U3,差分-单端电路包括巴伦变压器T1;

滤波器模块1包括10.7M陶瓷滤波器U4构成的滤波电路;

上变频模块包括用于变换信号频率的、经过阻抗匹配的无源混频器U5和用于根据收到的信息生成信号频率的直接数字式频率合成器U9,直接数字式频率合成器U9的频率输出端与无源混频器U5的频率接收端连接;

滤波器模块2包括17阶切比雪夫I型滤波器经高低通级联构成的、经过配置输入阻抗和输出阻抗的无源带通滤波器电路;

放大器模块包括射频功率放大器U6经过配置输入阻抗和输出阻抗构成的高频功率放大电路。

2.根据权利要求1所述的一种双路信号同传的FM调制发射系统,其特征在于:模数转换模块1还包括用作反馈电阻的第一电阻R1和第八电阻R8、用于增益设置的第四电阻R4和第七电阻R7、用于阻抗匹配的第二电阻R2,以及用于一阶低通滤波的第五电阻R5、第六电阻R6、第三电容C3和第五电容C5;第一电阻R1并联在第一差分放大器U2的引脚1和引脚4之间,第八电阻R8并联在第一差分放大器U2的引脚5和引脚8之间;第一差分放大器U2的引脚1通过串联第四电阻R4连接输入信号INPUT;第二电阻R2的一端连接输入信号INPUT,另一端连接信号地GND;第七电阻R7的一端连接第一差分放大器U2的引脚8,另一端连接信号地GND;第一差分放大器U2的引脚4通过串联第五电阻R5连接第一模数转换器U8的IN引脚;第三电容C3的一端连接第一模数转换器U8的IN引脚,另一端连接信号地GND;第一差分放大器U2的引脚5通过串联第六电阻R6连接第一模数转换器U8的/IN引脚;第五电容C5的一端连接第一模数转换器U8的/IN引脚,另一端连接信号地GND;第一模数转换器U8还包括分别用于输出12位数字信号的引脚B1、引脚B2、引脚B3、引脚B4、引脚B5、引脚B6、引脚B7、引脚B8、引脚B9、引脚B10、引脚B11和引脚B12。

3.根据权利要求2所述的一种双路信号同传的FM调制发射系统,其特征在于:模数转换模块2还包括用作反馈电阻的第一-二电阻R1-2和第八-二电阻R8-2、用于增益设置的第四-二电阻R4-2和第七-二电阻R7-2、用于阻抗匹配的第二-二电阻R2-2,以及用于一阶低通滤波的第五-二电阻R5-2、第六-二电阻R6-2、第三-二电容C3-2和第五-二电容C5-2;第一-二电阻R1-2并联在第二差分放大器U2-2的引脚1和引脚4之间,第八-二电阻R8-2并联在第二差分放大器U2-2的引脚5和引脚8之间;第二差分放大器U2-2的引脚1通过串联第四-二电阻R4-2连接输入信号INPUT2;第二-二电阻R2-2的一端连接输入信号INPUT2,另一端连接信号地GND;第七-二电阻R7-2的一端连接第二差分放大器U2-2的引脚8,另一端连接信号地GND;第二差分放大器U2-2的引脚4通过串联第五-二电阻R5-2连接第二模数转换器U8-2的IN引脚;第三-二电容C3-2的一端连接第二模数转换器U8-2的IN引脚,另一端连接信号地GND;第二差分放大器U2-2的引脚5通过串联第六-二电阻R6-2连接第二模数转换器U8-2的/IN引脚;第五-二电容C5-2的一端连接第二模数转换器U8-2的/IN引脚,另一端连接信号地GND;第二模数转换器U8-2还包括分别用于输出12位数字信号的引脚B1~引脚B12。

4.根据权利要求3所述的一种双路信号同传的FM调制发射系统,其特征在于:FPGA芯片U7的IO2口~IO13口依次与第一模数转换器U8的B1口~B12口连接,FPGA芯片U7的IO14口~IO25口依次与第二模数转换器U8-2的B1口~B12口连接;FPGA芯片U7的IO1口分别与第一模数转换器U8的CLK口和第二模数转换器U8-2的CLK口连接;FPGA芯片U7还包括用于依次输出FM调制信号的IO51口~IO38口,IO51口~IO38口的端口序号为倒序自然数排列。

5.根据权利要求4所述的一种双路信号同传的FM调制发射系统,其特征在于:数模转换器U3的BIT1引脚~BIT14引脚依次与FPGA芯片U7的IO51口~IO38口连接,数模转换器U3的CLK引脚与FPGA芯片U7的IO52口连接,数模转换器U3的IOUT引脚和*IOUT引脚分别与巴伦变压器T1的SECONDARY DOT引脚和SECONDARY引脚连接,巴伦变压器T1还包括用于输出信号OUTPUT1的PRIMARY引脚。

6.根据权利要求5所述的一种双路信号同传的FM调制发射系统,其特征在于:滤波器模块1还包括第十电阻R10和第十一电阻R11,10.7M陶瓷滤波器U4的IN引脚串联第十电阻R10后与巴伦变压器T1的PRIMARY引脚连接,10.7M陶瓷滤波器U4还包括用于输出信号OUTPUT2的OUT引脚,第十一电阻R11并联在OUT引脚与信号地GND之间。

7.根据权利要求6所述的一种双路信号同传的FM调制发射系统,其特征在于:上变频模块还包括用于阻抗匹配的第十二电阻R12和第十三电阻R13;无源混频器U5的RF引脚串联第十三电阻R13后与10.7M陶瓷滤波器U4的OUT引脚连接;第十二电阻R12的一端与无源混频器U5的IF引脚连接,第十二电阻R12的另一端输出信号OUTPUT3;直接数字式频率合成器U9的IN引脚与FPGA芯片U7的IO26口连接,直接数字式频率合成器U9的OUT引脚与无源混频器U5的LO引脚连接。

8.根据权利要求7所述的一种双路信号同传的FM调制发射系统,其特征在于:滤波器模块2还包括依次串联的第一电感L1、第二电感L2、第三电感L3、第四电感L4、第五电感L5、第六电感L6、第七电感L7、第八电感L8、第九电感L9、第十电感L10和第十一电感L11,

以及一端连接第一电感L1与第二电感L2的连接点、另一端连接信号地GND的第二十一电容C21,

一端连接第二电感L2与第三电感L3的连接点、另一端连接信号地GND的第二十二电容C22,

一端连接第三电感L3与第四电感L4的连接点、另一端连接信号地GND的第二十三电容C23,

一端连接第四电感L4与第五电感L5的连接点、另一端连接信号地GND的第二十四电容C24,

一端连接第五电感L5与第六电感L6的连接点、另一端连接信号地GND的第二十五电容C25,

一端连接第六电感L6与第七电感L7的连接点、另一端连接信号地GND的第二十六电容C26,

一端连接第七电感L7与第八电感L8的连接点、另一端连接信号地GND的第二十七电容C27,

一端连接第八电感L8与第九电感L9的连接点、另一端连接信号地GND的第二十八电容C28,

一端连接第九电感L9与第十电感L10的连接点、另一端连接信号地GND的第二十九电容C29,

一端连接第十电感L10与第十一电感L11的连接点、另一端连接信号地GND的第三十电容C30,

一端连接第十一电感L11的另一端、另一端连接信号地GND的第三十一电容C31;

第一电感L1不与第二十一电容C21连接的一端连接第十二电阻R12的另一端,第十一电感L11与第三十一电容C31的连接点输出信号OUTPUT4。

9.根据权利要求8所述的一种双路信号同传的FM调制发射系统,其特征在于:放大器模块还包括用于配置输入阻抗的第十四电阻R14、第十四电感L14和第三十五电容C35,以及用于配置输出阻抗的第十三电感L13和第三十四电容C34;第三十五电容C35的一端连接射频功率放大器U6的RF IN引脚,第三十五电容C35的另一端和第十四电感L14的一端共同与第十一电感L11和第三十一电容C31的连接点连接;第十四电感L14的另一端连接第十四电阻R14的一端;第十四电阻R14的另一端连接信号地GND;

第十三电感L13的一端连接射频功率放大器U6的RF OUT引脚,另一端连接第三十四电容C34的一端;第三十四电容C34的另一端输出信号OUT PUT5;射频功率放大器U6的2引脚与FPGA芯片U7的IO29口连接。

10.根据权利要求1所述的一种双路信号同传的FM调制发射系统,其特征在于:还包括用于采集用户输入信息的按键模块,按键模块的按键信号输出端与控制模块的按键信号输入端连接。

说明书

技术领域

本实用新型属于高频仪器技术领域,具体涉及一种双路信号同传的FM调制发射系统。

背景技术

调频(FM)信号,是通过基带信号控制载波的频率变化而得到的一种易于传输和发射的信号,其被广泛应用在无线广播、卫星通讯、短距离传呼机和蜂窝移动电话系统中。FM信号可通过软件调制和硬件调制进行,硬件方法成本低廉,但是要实现更高级的调制手段,所需电路过于复杂;而软件方法则更为灵活方便,其适用环境更为宽泛。

调制FM信号的方法包括直接调频和间接调频。直接调频可以方便地实现调频,但是缺点在于频率稳定度不高,频偏较大,传输中容易因为频率漂变,使得接收端信号失真;间接调频经过多次混频和倍频,频率稳定度好,但结构较复杂。

目前,市场对高质量语音传输的需求在不断提高,立体声正逐步取代传统的单声道语音信号。解决立体声传输问题的关键在于实现双路语音同传,即实现语音信号的复用传输;实现复用主要有两类方法,时分复用和频分复用。虽然时分复用较为节电,能够最大化使用带宽,但是其发射端和接收端需要周期性校时;而频分复用信道复用率高,且所有子信道以并行的方式传输信号,因而频分复用应用更广泛。

实用新型内容

本实用新型要解决的技术问题是:提供一种双路信号同传的FM调制发射系统,用于实现稳定传输双路语音信号的功能。

本实用新型为解决上述技术问题所采取的技术方案为:一种双路信号同传的FM调制发射系统,包括分别用于将两路语音电压信号转换为数字信号的模数转换模块1和模数转换模块2,用于输出FM载波频率和发射功率的控制模块,用于将FM数字信号转换为FM模拟信号的数模转换模块,用于滤除包括数字噪声的干扰的滤波器模块1,用于将中频段的FM模拟信号上变频至高频段的FM模拟信号的上变频模块,用于滤除包括寄生通道干扰和镜像频率的干扰的滤波器模块2,用于放大信号功率的放大器模块,和用于发射信号的天线模块;模数转换模块1和模数转换模块2的信号输出端分别与控制模块的信号输入端连接,控制模块、数模转换模块、滤波器模块1、上变频模块、滤波器模块2、放大器模块和天线模块依次串联;控制模块的控制端分别与上变频模块和放大器模块的受控端连接,控制模块的时钟输出端分别与模数转换模块1、模数转换模块2和数模转换模块的时钟输入端连接;模数转换模块1包括依次串联的单端-差分电路和差分-数字电路;单端-差分电路由第一差分放大器U2、反馈电阻、增益设置电阻和终端电阻经过配置放大倍数、配置输入阻抗、采用直流耦合构成;差分-数字电路由第一模数转换器U8经过限制输入带宽和配置时钟后构成;模数转换模块2包括依次串联的单端-差分电路和差分-数字电路;单端-差分电路由第二差分放大器U2-2、反馈电阻、增益设置电阻和终端电阻经过配置放大倍数、配置输入阻抗、采用直流耦合构成;差分-数字电路由第二模数转换器U8-2经过限制输入带宽和配置时钟后构成;控制模块包括FPGA芯片U7及其外围元件构成的电路,FPGA芯片U7的内部固化有依次串联的用于对一路语音信号做AM数字调制并与另一路语音信号相加得到基带信号的频分复用模块,和用于通过基带信号控制正弦查找表的相位控制字生成FM数字信号的FM数字调制模块;数模转换模块包括依次串联的数字-差分电路和差分-单端电路,数字-差分电路包括数模转换器U3,差分-单端电路包括巴伦变压器T1;滤波器模块1包括10.7M陶瓷滤波器U4构成的滤波电路;上变频模块包括用于变换信号频率的、经过阻抗匹配的无源混频器U5和用于根据收到的信息生成信号频率的直接数字式频率合成器U9,直接数字式频率合成器U9的频率输出端与无源混频器U5的频率接收端连接;滤波器模块2包括17阶切比雪夫I型滤波器经高低通级联构成的、经过配置输入阻抗和输出阻抗的无源带通滤波器电路;放大器模块包括射频功率放大器U6经过配置输入阻抗和输出阻抗构成的高频功率放大电路。

按上述方案,模数转换模块1还包括用作反馈电阻的第一电阻R1和第八电阻R8、用于增益设置的第四电阻R4和第七电阻R7、用于阻抗匹配的第二电阻R2,以及用于一阶低通滤波的第五电阻R5、第六电阻R6、第三电容C3和第五电容C5;第一电阻R1并联在第一差分放大器U2的引脚1和引脚4之间,第八电阻R8并联在第一差分放大器U2的引脚5和引脚8之间;第一差分放大器U2的引脚1通过串联第四电阻R4连接输入信号INPUT;第二电阻R2的一端连接输入信号INPUT,另一端连接信号地GND;第七电阻R7的一端连接第一差分放大器U2的引脚8,另一端连接信号地GND;第一差分放大器U2的引脚4通过串联第五电阻R5连接第一模数转换器U8的IN引脚;第三电容C3的一端连接第一模数转换器U8的IN引脚,另一端连接信号地GND;第一差分放大器U2的引脚5通过串联第六电阻R6连接第一模数转换器U8的/IN引脚;第五电容C5的一端连接第一模数转换器U8的/IN引脚,另一端连接信号地GND;第一模数转换器U8还包括分别用于输出12位数字信号的引脚B1、引脚B2、引脚B3、引脚B4、引脚B5、引脚B6、引脚B7、引脚B8、引脚B9、引脚B10、引脚B11和引脚B12。

进一步的,模数转换模块2还包括用作反馈电阻的第一-二电阻R1-2和第八-二电阻R8-2、用于增益设置的第四-二电阻R4-2和第七-二电阻R7-2、用于阻抗匹配的第二-二电阻R2-2,以及用于一阶低通滤波的第五-二电阻R5-2、第六-二电阻R6-2、第三-二电容C3-2和第五-二电容C5-2;第一-二电阻R1-2并联在第二差分放大器U2-2的引脚1和引脚4之间,第八-二电阻R8-2并联在第二差分放大器U2-2的引脚5和引脚8之间;第二差分放大器U2-2的引脚1通过串联第四-二电阻R4-2连接输入信号INPUT2;第二-二电阻R2-2的一端连接输入信号INPUT2,另一端连接信号地GND;第七-二电阻R7-2的一端连接第二差分放大器U2-2的引脚8,另一端连接信号地GND;第二差分放大器U2-2的引脚4通过串联第五-二电阻R5-2连接第二模数转换器U8-2的IN引脚;第三-二电容C3-2的一端连接第二模数转换器U8-2的IN引脚,另一端连接信号地GND;第二差分放大器U2-2的引脚5通过串联第六-二电阻R6-2连接第二模数转换器U8-2的/IN引脚;第五-二电容C5-2的一端连接第二模数转换器U8-2的/IN引脚,另一端连接信号地GND;第二模数转换器U8-2还包括分别用于输出12位数字信号的引脚B1~引脚B12。

进一步的,FPGA芯片U7的IO2口~IO13口依次与第一模数转换器U8的B1口~B12口连接,FPGA芯片U7的IO14口~IO25口依次与第二模数转换器U8-2的B1口~B12口连接;FPGA芯片U7的IO1口分别与第一模数转换器U8的CLK口和第二模数转换器U8-2的CLK口连接;FPGA芯片U7还包括用于依次输出FM调制信号的IO51口~IO38口,IO51口~IO38口的端口序号为倒序自然数排列。

进一步的,数模转换器U3的BIT1引脚~BIT14引脚依次与FPGA芯片U7的IO51口~IO38口连接,数模转换器U3的CLK引脚与FPGA芯片U7的IO52口连接,数模转换器U3的IOUT引脚和*IOUT引脚分别与巴伦变压器T1的SECONDARY DOT引脚和SECONDARY引脚连接,巴伦变压器T1还包括用于输出信号OUTPUT1的PRIMARY引脚。

进一步的,滤波器模块1还包括第十电阻R10和第十一电阻R11,10.7M陶瓷滤波器U4的IN引脚串联第十电阻R10后与巴伦变压器T1的PRIMARY引脚连接,10.7M陶瓷滤波器U4还包括用于输出信号OUTPUT2的OUT引脚,第十一电阻R11并联在OUT引脚与信号地GND之间。

进一步的,上变频模块还包括用于阻抗匹配的第十二电阻R12和第十三电阻R13;无源混频器U5的RF引脚串联第十三电阻R13后与10.7M陶瓷滤波器U4的OUT引脚连接;第十二电阻R12的一端与无源混频器U5的IF引脚连接,第十二电阻R12的另一端输出信号OUTPUT3;直接数字式频率合成器U9的IN引脚与FPGA芯片U7的IO26口连接,直接数字式频率合成器U9的OUT引脚与无源混频器U5的LO引脚连接。

进一步的,滤波器模块2还包括依次串联的第一电感L1、第二电感L2、第三电感L3、第四电感L4、第五电感L5、第六电感L6、第七电感L7、第八电感L8、第九电感L9、第十电感L10和第十一电感L11,以及一端连接第一电感L1与第二电感L2的连接点、另一端连接信号地GND的第二十一电容C21,一端连接第二电感L2与第三电感L3的连接点、另一端连接信号地GND的第二十二电容C22,一端连接第三电感L3与第四电感L4的连接点、另一端连接信号地GND的第二十三电容C23,一端连接第四电感L4与第五电感L5的连接点、另一端连接信号地GND的第二十四电容C24,一端连接第五电感L5与第六电感L6的连接点、另一端连接信号地GND的第二十五电容C25,一端连接第六电感L6与第七电感L7的连接点、另一端连接信号地GND的第二十六电容C26,一端连接第七电感L7与第八电感L8的连接点、另一端连接信号地GND的第二十七电容C27,一端连接第八电感L8与第九电感L9的连接点、另一端连接信号地GND的第二十八电容C28,一端连接第九电感L9与第十电感L10的连接点、另一端连接信号地GND的第二十九电容C29,一端连接第十电感L10与第十一电感L11的连接点、另一端连接信号地GND的第三十电容C30,一端连接第十一电感L11的另一端、另一端连接信号地GND的第三十一电容C31;第一电感L1不与第二十一电容C21连接的一端连接第十二电阻R12的另一端,第十一电感L11与第三十一电容C31的连接点输出信号OUTPUT4。

进一步的,放大器模块还包括用于配置输入阻抗的第十四电阻R14、第十四电感L14和第三十五电容C35,以及用于配置输出阻抗的第十三电感L13和第三十四电容C34;第三十五电容C35的一端连接射频功率放大器U6的RF IN引脚,第三十五电容C35的另一端和第十四电感L14的一端共同与第十一电感L11和第三十一电容C31的连接点连接;第十四电感L14的另一端连接第十四电阻R14的一端;第十四电阻R14的另一端连接信号地GND;第十三电感L13的一端连接射频功率放大器U6的RF OUT引脚,另一端连接第三十四电容C34的一端;第三十四电容C34的另一端输出信号OUT PUT5;射频功率放大器U6的2引脚与FPGA芯片U7的IO29口连接。

按上述方案,还包括用于采集用户输入信息的按键模块,按键模块的按键信号输出端与控制模块的按键信号输入端连接。

本实用新型的有益效果为:

1.本实用新型的一种双路信号同传的FM调制发射系统通过双路信号频分复用和FM数字调制,解决了传统FM调制领域难以实现的双路信号的发射的问题,实现了FM载波频率和FM发射功率的调节功能,实现了稳定传输双路语音信号的功能。

2.本实用新型能够通过按键输入调节FM信号的载波频率和发射功率,操作方便。

3.本实用新型结构简单、稳定性好、抗干扰强,应用范围广。

附图说明

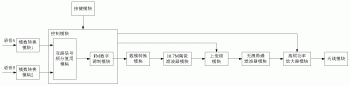

图1是本实用新型实施例的功能框图。

图2是本实用新型实施例的模数转换模块电路图。

图3是本实用新型实施例的控制模块电路图。

图4是本实用新型实施例的数模转换模块电路图。

图5是本实用新型实施例的10.7MHz陶瓷滤波器模块电路图。

图6是本实用新型实施例的上变频模块电路图。

图7是本实用新型实施例的无源带通滤波器模块电路图。

图8是本实用新型实施例的高频功率放大器模块电路图。

图9是本实用新型实施例的按键模块电路图。

具体实施方式

下面结合附图和具体实施方式对本实用新型作进一步详细的说明。

参见图1,本实用新型的实施例包括模数转换模块1、模数转换模块2、控制模块、数模转换模块、10.7M陶瓷滤波器模块、上变频模块、无源带通滤波器模块、高频功率放大器模块,以及用于发射高频段的FM信号的天线模块和用于采集用户输入信息的按键模块。模数转换模块1和模数转换模块2的信号输出端分别与双路信号频分复用模块的信号输入端连接,控制模块、数模转换模块、10.7M陶瓷滤波器模块、上变频模块、无源带通滤波器模块、高频功率放大器模块和天线模块依次串联;控制模块的控制端分别与上变频模块和高频功率放大器模块的受控端连接,控制模块的时钟输出端分别与模数转换模块1、模数转换模块2和数模转换模块的时钟输入端连接,按键模块的按键信号输出端与控制模块的按键信号输入端连接。

参见图2,模数转换模块1用于将一路语音电压信号转换为数字信号并输出给微处理器进行一系列数字调制处理;由于信号为语音信号,故采样频率设置为10KHz。模数转换模块1包括依次串联的单端-差分电路和差分-数字电路;单端-差分电路由第一差分放大器U2、反馈电阻、增益设置电阻和终端电阻经过配置放大倍数、配置输入阻抗、采用直流耦合构成,第一差分放大器U2采用THS4151芯片;差分-数字电路由第一模数转换器U8经过限制输入带宽和配置时钟后构成,第一模数转换器U8采用ADS805芯片;模数转换模块1还包括用作反馈电阻的第一电阻R1和第八电阻R8、用于增益设置的第四电阻R4和第七电阻R7、用于阻抗匹配的第二电阻R2,以及用于一阶低通滤波的第五电阻R5、第六电阻R6、第三电容C3和第五电容C5;第一电阻R1并联在第一差分放大器U2的引脚1和引脚4之间,第八电阻R8并联在第一差分放大器U2的引脚5和引脚8之间;第一差分放大器U2的引脚1通过串联第四电阻R4连接输入信号INPUT;第二电阻R2的一端连接输入信号INPUT,另一端连接信号地GND;第七电阻R7的一端连接第一差分放大器U2的引脚8,另一端连接信号地GND;第一差分放大器U2的引脚4通过串联第五电阻R5连接第一模数转换器U8的IN引脚;第三电容C3的一端连接第一模数转换器U8的IN引脚,另一端连接信号地GND;第一差分放大器U2的引脚5通过串联第六电阻R6连接第一模数转换器U8的/IN引脚;第五电容C5的一端连接第一模数转换器U8的/IN引脚,另一端连接信号地GND;第一模数转换器U8还包括分别用于输出12位数字信号的引脚B1、引脚B2、引脚B3、引脚B4、引脚B5、引脚B6、引脚B7、引脚B8、引脚B9、引脚B10、引脚B11和引脚B12。模数转换模块1还包括用于通断信号通路、方便调试的第三电阻R3,用于滤波的第一电容C1、第二电容C2、第四电容C4、第六电容C6、第七电容C7、第八电容C8、第九电容C9、第十电容C10、第十一电容C11、第十二电容C12,以及用于暂时存放控制模块发送的时钟数据、对高速工作的控制模块与慢速工作的模数转换模块1起协调和缓冲作用、实现数据同步传送的数控缓冲器U1,数控缓冲器U1采用SN74LV1T126DBVRG4缓冲器芯片,数控缓冲器U1的A引脚与FPGA的IO1引脚连接,数控缓冲器U1的Y引脚与第一模数转换器U8的CLK引脚连接。

模数转换模块2用于将另一路语音电压信号转换为数字信号并输出给微处理器进行一系列数字调制处理,采样频率同样确定为10KHz。模数转换模块2包括依次串联的单端-差分电路和差分-数字电路;单端-差分电路由第二差分放大器U2-2、反馈电阻、增益设置电阻和终端电阻经过配置放大倍数、配置输入阻抗、采用直流耦合构成,第二差分放大器U2-2采用THS4151芯片;差分-数字电路由第二模数转换器U8-2经过限制输入带宽和配置时钟后构成,第二模数转换器U8-2采用ADS805芯片;模数转换模块2还包括用作反馈电阻的第一-二电阻R1-2和第八-二电阻R8-2、用于增益设置的第四-二电阻R4-2和第七-二电阻R7-2、用于阻抗匹配的第二-二电阻R2-2,以及用于一阶低通滤波的第五-二电阻R5-2、第六-二电阻R6-2、第三-二电容C3-2和第五-二电容C5-2;第一-二电阻R1-2并联在第二差分放大器U2-2的引脚1和引脚4之间,第八-二电阻R8-2并联在第二差分放大器U2-2的引脚5和引脚8之间;第二差分放大器U2-2的引脚1通过串联第四-二电阻R4-2连接输入信号INPUT2;第二-二电阻R2-2的一端连接输入信号INPUT2,另一端连接信号地GND;第七-二电阻R7-2的一端连接第二差分放大器U2-2的引脚8,另一端连接信号地GND;第二差分放大器U2-2的引脚4通过串联第五-二电阻R5-2连接第二模数转换器U8-2的IN引脚;第三-二电容C3-2的一端连接第二模数转换器U8-2的IN引脚,另一端连接信号地GND;第二差分放大器U2-2的引脚5通过串联第六-二电阻R6-2连接第二模数转换器U8-2的/IN引脚;第五-二电容C5-2的一端连接第二模数转换器U8-2的/IN引脚,另一端连接信号地GND;第二模数转换器U8-2还包括分别用于输出12位数字信号的引脚B1~引脚B12。模数转换模块2还包括用于暂时存放控制模块发送的时钟数据、对高速工作的控制模块与慢速工作的模数转换模块2起协调和缓冲作用、实现数据同步传送的第二数控缓冲器U1-2,第二数控缓冲器U1-2采用SN74LV1T126DBVRG4缓冲器芯片,第二数控缓冲器U1-2的A引脚与FPGA的IO1引脚连接,第二数控缓冲器U1-2的Y引脚与第二模数转换器U8-2的CLK引脚连接。模数转换模块2的其他分立电路元件配置、引脚设置与模数转换模块1的分立电路元件配置、引脚设置完全相同。

参见图3,控制模块包括FPGA芯片U7及其外围元件构成的电路,FPGA芯片U7采用Altera公司Cyclone IV系列的型号为EP4CE40F23C8的高速FPGA;FPGA芯片U7包括用于对一路语音信号做AM数字调制搬移到高频段信道,并与另一路语音信号相加,组成带有两个信号频段的新的基带信号的双路信号频分复用模块,和用于通过基带信号控制正弦查找表的相位控制字,将输入的基带信号从10.7MHz中频调制为FM信号,生成载波频率为10.7MHz的FM数字信号的FM数字调制模块;通过对FPGA芯片U7的熔丝位进行编辑,双路信号频分复用模块和FM数字调制模块依次串联并固化在FPGA芯片U7内部。控制模块还用于输出AD和DA的时钟频率、FM载波频率和发射功率。FPGA芯片U7的IO2口~IO13口依次与第一模数转换器U8的B1口~B12口连接,FPGA芯片U7的IO14口~IO25口依次与第二模数转换器U8-2的B1口~B12口连接;FPGA芯片U7还包括用于依次输出FM调制信号的IO51口~IO38口,IO51口~IO38口的端口序号为倒序自然数排列;FPGA芯片U7的VCC引脚连接+5V,GND引脚连接信号地GND。

参见图4,数模转换模块用于将10.7MHz的FM数字信号转换为10.7MHz的FM模拟信号,转换频率为100MHz。数模转换模块包括依次串联的数字-差分电路和差分-单端电路;数字-差分电路包括数模转换器U3,数模转换器U3采用DAC904_DW_28芯片;差分-单端电路包括巴伦变压器T1,巴伦变压器T1采用ADT1-1WT+芯片;数模转换器U3的BIT1引脚~BIT14引脚依次与FPGA芯片U7的IO51口~IO38口连接,数模转换器U3的CLK引脚与FPGA芯片U7的IO52口连接,数模转换器U3的IOUT引脚和*IOUT引脚分别与巴伦变压器T1的SECONDARY DOT引脚和SECONDARY引脚连接,巴伦变压器T1还包括用于输出信号OUTPUT1的PRIMARY引脚。数模转换模块还包括用于滤波的第十三电容C13、第十七电容C17、第十八电容C18、第十四电容C14、第十五电容C15、第十六电容C16,以及第九电阻R9;数模转换器U3的VD+引脚连接电源DVDD,DGND引脚连接信号地DGND,VA+引脚连接电源+5V;巴伦变压器T1的PRIMARY DOT引脚连接信号地GND。

参见图5,10.7M陶瓷滤波器模块用于滤除包括数字噪声的干扰得到信噪比较高的FM信号。10.7M陶瓷滤波器模块包括10.7M陶瓷滤波器U4构成的滤波电路,10.7M陶瓷滤波器U4采用SFECF10M7GA00-R0芯片,该陶瓷滤波器的中心频率为10.7MHz,3dB频带宽度为230KHz,阻带宽范围为510KHz,能够有效滤除频带外的数字噪声得到10.7MHz的FM信号;10.7MHz陶瓷滤波器模块还包括第十电阻R10和第十一电阻R11,10.7M陶瓷滤波器U4的IN引脚串联第十电阻R10后与巴伦变压器T1的PRIMARY引脚连接,10.7M陶瓷滤波器U4还包括用于输出信号OUTPUT2的OUT引脚,第十一电阻R11并联在OUT引脚与信号地GND之间。10.7MHz陶瓷滤波器模块还包括用于滤波的第十九电容C19,10.7M陶瓷滤波器U4的GND引脚连接信号地GND。

参见图6,上变频模块用于将中频段的10.7MHz的FM模拟信号上变频至高频段的10.7MHz的FM模拟信号,实现FM载波频率的准确可调。上变频模块包括用于变换信号频率的、经过阻抗匹配的无源混频器U5和用于根据收到的信息生成信号频率的直接数字式频率合成器(Direct Digital Synthesizer,DDS)U9,直接数字式频率合成器U9的频率输出端与无源混频器U5的频率接收端连接。无源混频器U5采用ADE-2+芯片,该混频器隔离度达47dB,满足本征信号为+7dBm的要求;直接数字式频率合成器U9采用AD9958芯片,直接数字式频率合成器U9根据控制模块发送的信息生成信号频率并发送至无源混频器U5,从而改变本振频率,将FM信号上变频至高频段,实现频谱的搬移,动态范围广,隔离度高,噪声低;上变频模块还包括用于阻抗匹配的第十二电阻R12和第十三电阻R13;无源混频器U5的RF引脚串联第十三电阻R13后与10.7M陶瓷滤波器U4的OUT引脚连接;第十二电阻R12的一端与无源混频器U5的IF引脚连接,第十二电阻R12的另一端输出信号OUTPUT3;直接数字式频率合成器U9的IN引脚与FPGA芯片U7的IO26口连接,直接数字式频率合成器U9的OUT引脚与无源混频器U5的LO引脚连接。上变频模块还包括用于滤波的第二十电容C20;无源混频器U5的GROUND引脚和直接数字式频率合成器U9的GND引脚均连接信号地GND,直接数字式频率合成器U9的VCC引脚连接电源+5V。

参见图7,无源带通滤波器模块用于滤除包括寄生通道干扰和镜像频率,防止对后续信号处理造成干扰,同时降低后级高频功放的功耗。无源带通滤波器模块包括17阶带内波动0.2dB的切比雪夫I型滤波器经高低通级联构成的、经过配置输入阻抗和输出阻抗均为50欧的无源带通滤波器电路,与前后级电路严格匹配;无源带通滤波器电路的集总参数模型包括依次串联的第一电感L1、第二电感L2、第三电感L3、第四电感L4、第五电感L5、第六电感L6、第七电感L7、第八电感L8、第九电感L9、第十电感L10和第十一电感L11,以及一端连接第一电感L1与第二电感L2的连接点、另一端连接信号地GND的第二十一电容C21,一端连接第二电感L2与第三电感L3的连接点、另一端连接信号地GND的第二十二电容C22,一端连接第三电感L3与第四电感L4的连接点、另一端连接信号地GND的第二十三电容C23,一端连接第四电感L4与第五电感L5的连接点、另一端连接信号地GND的第二十四电容C24,一端连接第五电感L5与第六电感L6的连接点、另一端连接信号地GND的第二十五电容C25,一端连接第六电感L6与第七电感L7的连接点、另一端连接信号地GND的第二十六电容C26,一端连接第七电感L7与第八电感L8的连接点、另一端连接信号地GND的第二十七电容C27,一端连接第八电感L8与第九电感L9的连接点、另一端连接信号地GND的第二十八电容C28,一端连接第九电感L9与第十电感L10的连接点、另一端连接信号地GND的第二十九电容C29,一端连接第十电感L10与第十一电感L11的连接点、另一端连接信号地GND的第三十电容C30,一端连接第十一电感L11的另一端、另一端连接信号地GND的第三十一电容C31;第一电感L1不与第二十一电容C21连接的一端连接第十二电阻R12的另一端,第十一电感L11与第三十一电容C31的连接点输出信号OUTPUT4。

参见图8,高频功率放大器模块用于根据收到的信息放大FM信号功率,提高信噪比,便于后级天线发射和增大发射距离。高频功率放大器模块包括射频功率放大器U6经过配置输入阻抗和输出阻抗构成的高频功率放大电路,射频功率放大器U6采用RF3827,该芯片为通用、高性能、高线性度的射频功率放大器,噪声系数小于1.5dB,适用于作为低噪声放大器;RF3827芯片在提供20dB固定增益的同时带宽达1.5G,且能同时匹配50欧和75欧的系统,在本实用新型中采用50欧的阻抗匹配;高频功率放大器模块还包括用于配置输入阻抗的第十四电阻R14、第十四电感L14和第三十五电容C35,以及用于配置输出阻抗的第十三电感L13和第三十四电容C34;第三十五电容C35的一端连接射频功率放大器U6的RF IN引脚,第三十五电容C35的另一端和第十四电感L14的一端共同与第十一电感L11和第三十一电容C31的连接点连接;第十四电感L14的另一端连接第十四电阻R14的一端;第十四电阻R14的另一端连接信号地GND;第十三电感L13的一端连接射频功率放大器U6的RF OUT引脚,另一端连接第三十四电容C34的一端;第三十四电容C34的另一端与输出信号OUT PUT5;射频功率放大器U6的2引脚与FPGA芯片U7的IO29口连接用于接收控制模块发送的功率控制信息。高频功率放大器模块还包括用于滤波的第十二电感L12、第三十二电容C32和第三十三电容C33;第十二电感L12的一端连接射频功率放大器U6的RF OUT引脚,另一端与第三十二电容C32的一端、第三十三电容C33的一端共同连接电源+5V,第三十二电容C32和第三十三电容C33的另一端连接信号地GND;射频功率放大器U6的GND引脚连接信号地GND。

参见图9,按键模块用于采集用户的输入的键值并输出给控制模块以设定FM信号发射功率的大小,最小步进为1dB;按键模块采用4×4矩阵键盘;矩阵键盘的输出端P4.0~P4.7分别与FPGA芯片U7的IO37口~IO30口连接,IO37口~IO30口的端口序号为倒序自然数排列。

上述电路中使用的元器件的名称、规格型号和位号如表1所示:

表1

本实用新型的工作流程为:

双路语音电压信号分别通过两路模数转换器变为数字信号,输入FPGA进行数字调制,一路信号通过AM数字调制搬移到10kHz频率,与另一路信号相加得到基带信号,实现双路信号频分复用;将得到的新的基带信号通过FM数字调制转化为10.7MHz中频的FM数字信号,最终经数模转换器变为FM模拟信号,再经由上变频模块,混频至可键控调节的更高频率,经过高频功率放大器放大后,由天线发射。

以上实施例仅用于说明本实用新型的设计思想和特点,其目的在于使本领域内的技术人员能够了解本实用新型的内容并据以实施,本实用新型的保护范围不限于上述实施例。所以,凡依据本实用新型所揭示的原理、设计思路所作的等同变化或修饰,均在本实用新型的保护范围之内。

一种双路信号同传的FM调制发射系统专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0