专利摘要

本实用新型提供了一种守时系统主钟信号保持器,数据采集单元将主备钟差、主钟与第三方钟钟差、备钟与第三方钟钟差以及守时钟组比对数据发送至数据处理单元;数据处理单元计算得到主钟驾驭量和备钟驾驭量,同时检测原子钟异常情况;控制与显示单元向主备钟的相位微调仪发送主钟驾驭量和备钟驾驭量,主钟故障时向锁相环电路发送保持指令,并切换到备钟;功率合成器将主钟和备钟的输出信号并行连接后输入具有采样电压存储控制功能的锁相环,并将锁相环的输出作为输出信号。本实用新型能够实时检测主钟故障,实现高精度主钟时间频率信号的输出的连续性和一致性。

权利要求

1.一种守时系统主钟信号保持器,包括数据采集单元、数据处理单元、控制与显示单元、输出时间频率信号保持单元,其特征在于:所述的数据采集单元采集主钟时间频率信号、备钟时间频率信号、第三方钟时间频率信号和守时钟组比对数据,对比得到主备钟差、主钟与第三方钟钟差、备钟与第三方钟钟差,与守时钟组比对数据共同发送至数据处理单元;数据处理单元计算得到主钟驾驭量和备钟驾驭量,同时检测原子钟异常情况,将主钟驾驭量、备钟驾驭量、原子钟异常检测结果和钟组比对数据发送到控制与显示单元;控制与显示单元向主备钟的相位微调仪分别发送主钟驾驭量和备钟驾驭量,主钟故障时向锁相环电路发送保持指令,并切换到备钟;输出频率信号保持单元通过功率合成器将主钟和备钟的输出信号并行连接后输入具有采样电压存储控制功能的锁相环,并将锁相环的输出作为主钟信号保持器的输出信号。

2.根据权利要求1所述的守时系统主钟信号保持器,其特征在于:所述数据采集单元包括多通道相位比较电路、数据存储模块以及网络数据读取接口,数据输出接口;多通道相位比较电路根据主钟时间频率信号、备钟时间频率信号和第三方钟时间频率信号得到主备钟差、主钟与第三方钟钟差以及备钟与第三方钟钟差;数据存储模块将多通道相位比较系统的输出进行存储;网络数据读取接口读取守时钟组比对数据,数据输出接口将守时钟组比对数据输出到数据处理单元。

3.根据权利要求1所述的守时系统主钟信号保持器,其特征在于:所述控制与显示单元包括阵列键盘、配置模块、液晶屏及显示控制模块和时间保持控制模块;配置模块接收阵列键盘输入的配置参数信息;液晶屏及显示控制模块通过液晶屏显示主备钟差图和原子钟故障信息;时间保持控制模块向主备钟的相位微调仪发送驾驭控制量,主钟故障时向切换开关发送切换指令,向锁相环电路发送保持指令。

说明书

技术领域

本发明涉及一种守时系统主钟时间频率信号的保持装置,属于时间频率技术领域,尤其是用于守时系统主钟信号的驾驭与保持,为精密时间用户提供连续、一致的高精度时间频率信号。

背景技术

精密时间是国家重要的战略资源,精密时间/频率信号在战略武器实验、星箭发射、导航定位等现代国防、国民经济建设,以及科技领域得到越来越广泛的应用,而守时系统的建立与保持是时间工作的基础与核心。

守时系统通常由具有一定规模的钟组建立和维持,而其实时的标准时间频率物理信号由主钟系统提供。主钟系统由主钟和相位微调仪组成,通过相位微调仪对主钟的输出信号进行驾驭,提供实时的、高精度的时间频率信号。传统上,对主钟进行频率驾驭的参考是守时系统的时间尺度,具有一定的滞后性,因此对于主钟信号异常的判断也会有所延迟;当主钟出现异常情况,通过手动切换的方式更换一台主钟,传统方法对于关注标准时间频率信号准确度和中长期稳定度的守时要求几乎没有影响。然而随着科学技术的发展,日益众多的行业对守时系统提供的时间/频率信号提出了越来越高的要求,尤其是现代高技术领域和国防建设,如卫星导航定位(GNSS)系统、现代军事通信系统、航空航天系统等,主钟系统必须保持高精度实时输出信号的连续性和一致性。

主钟信号保持的关键是建立与主钟联系更加紧密的备份主钟系统,在主钟异常时可以迅速替代。美国海军天文台(USNO)为保证GPS的用时安全,在内部建立UTC(USNO MC#1)和UTC(USNO MC#2)互为备份,还在位于科罗拉多州的施里弗空军基建立异地备份系统USNO AMC。GALILEO导航系统的主钟系统是由一主一备两台氢钟HM1和HM2组成的。GLONASS导航系统的守时系统也有类似的设计。以GALILEO的主钟系统为例,备钟系统与主钟系统之间实时同步,检测主钟故障,并通过切换开关切换,从而达到主钟信号保持效果。系统构成包括了相位微调仪、比相仪、控制计算机、切换开关等若干设备并且需要它们之间协调工作,具有一定的复杂度,而采用切换开关的切换方法会对输出信号造成短暂中断和一定影响,如何实现无缝切换,保持主钟信号性能的方法也未在公开资料中批露,无法获得直接的可行性方案。

为了满足空间技术研究等多个行业对守时系统时间频率信号的连续性和一致性需求,需要建立主钟的备份系统,对系统进行集成化的设计,并且融入守时系统的时间尺度算法和频率驾驭技术,研究主备之间无缝切换的方法,实现守时系统的主钟时间频率信号的保持功能。

发明内容

为了克服现有技术的不足,本发明提供一种守时系统主钟信号保持器,采用集成化的设计,基于主备钟输入,实现主备钟的频率驾驭和时间同步,实时检测主钟的运行状态,在主钟故障时切换到备钟,经过锁相环电路保证高精度的时间频率的连续输出。

本发明解决其技术问题所采用的技术方案是:包括数据采集单元、数据处理单元、控制与显示单元、输出时间频率信号保持单元。

所述的数据采集单元采集主钟时间频率信号、备钟时间频率信号、第三方钟时间频率信号和守时钟组比对数据,对比得到主备钟差、主钟与第三方钟钟差、备钟与第三方钟钟差,与守时钟组比对数据共同发送至数据处理单元;数据处理单元计算得到主钟驾驭量和备钟驾驭量,同时检测原子钟异常情况,将主钟驾驭量、备钟驾驭量、原子钟异常检测结果和钟组比对数据发送到控制与显示单元;控制与显示单元向主备钟的相位微调仪分别发送主钟驾驭量和备钟驾驭量,主钟故障时向锁相环电路发送保持指令,并切换到备钟;输出频率信号保持单元通过功率合成器将主钟和备钟的输出信号并行连接后输入具有采样电压存储控制功能的锁相环,并将锁相环的输出作为主钟信号保持器的输出信号。

所述数据采集单元包括多通道相位比较电路、数据存储模块以及网络数据读取接口,数据输出接口。多通道相位比较电路根据主钟时间频率信号、备钟时间频率信号和第三方钟时间频率信号得到主备钟差、主钟与第三方钟钟差以及备钟与第三方钟钟差;数据存储模块将多通道相位比较系统的输出进行存储;网络数据读取接口读取守时钟组比对数据,数据输出接口将守时钟组比对数据输出到数据处理单元。

所述数据处理单元包括预处理模块、主钟驾驭量生成模块、备钟驾驭量生成模块和故障检测模块;预处理模块将主备钟差、主钟与第三方钟钟差、备钟与第三方钟钟差以及守时钟组比对数据进行粗差剔除和滤波;主钟驾驭量生成模块生成主钟驾驭量;备钟驾驭量生成模块生成备钟驾驭量;故障检测模块检测原子钟异常情况。

所述控制与显示单元包括阵列键盘、配置模块、液晶屏及显示控制模块和时间保持控制模块;配置模块接收阵列键盘输入的配置参数信息;液晶屏及显示控制模块通过液晶屏显示主备钟差图和原子钟故障信息;时间保持控制模块向主备钟的相位微调仪发送驾驭控制量,主钟故障时向切换开关发送切换指令,向锁相环电路发送保持指令。

本发明的有益效果是:能够驾驭主备钟信号同步并实时显示主备钟差曲线,实时检测主钟故障,控制锁相环电路,实现高精度主钟时间频率信号的输出的连续性和一致性。

本发明采用黑箱操作模式,主备钟同步功能、实时故障检测功能以及可以控制的锁相环电路保证了在主钟信号异常的情况下,能够智能化的自主保持输出时间频率信号稳定。

本发明设计的主备钟功率合成器,不仅可以保持主钟系统输出信号的连续性,而且可以使主钟系统输出信号的性能相对于单纯的主钟或备钟输出有所提高,其性能提高具体表现在频率稳定度的提高和相位噪声的降低。

本发明采用模块化的设计,各个模块均可独立运行,具备较强的可维护性与可扩展性。

附图说明

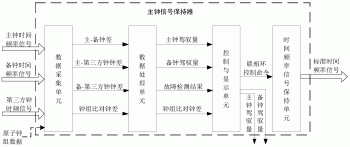

图1是本发明的系统结构框图;

图2是本发明的数据采集单元结构框图;

图3是本发明的数据处理单元结构框图;

图4是本发明的控制与显示单元结构框图;

图5是本发明的时间频率信号保持单元结构框图。

具体实施方式

下面结合附图和实施例对本发明进一步说明,本发明包括但不仅限于下述实施例。

本发明提供一种守时系统主钟信号保持器,在构建主备钟系统的基础上,通过主钟信号保持器保证主钟信号性能。本发明包括数据采集单元、数据处理单元、控制单元、输出时间频率信号保持单元。(1)数据采集单元采集主备钟差、主钟与第三方钟钟差、备钟与第三方钟钟差,通过网络获得钟组比对数据,向数据处理单元发送数据。(2)数据处理单元对数据进行预处理,计算主钟驾驭量,备钟驾驭量,检测原子钟异常情况,并将相关结果发送到控制与显示单元。(3)控制与显示单元根据数据处理单元的结果向主备钟的相位微调仪发送驾驭控制量,主钟故障时向切换开关发送切换指令,向锁相环电路发送保持指令,通过显示屏显示主备钟差图,显示原子钟故障信息,并可以配置相关参数。(4)输出频率信号保持单元通过功率合成器将主钟和备钟并行连接,将功合器的输出作为后置的具有采样电压存储控制功能的锁相环的输入,并将锁相环的输出作为主钟信号保持器的输出信号。

所述数据采集单元包括多通道相位比较电路、数据存储模块以及网络数据读取接口,数据输出接口。多通道相位比较系统用于获取主备钟差数据、主钟与第三方钟钟差数据以及备钟与第三方钟钟差数据;数据存储模块用于将多通道相位比较系统获得的数据近实时地按照指定数据格式存储在主钟信号保持器的数据存储区域;网络数据读取接口读取守时钟组比对数据,数据输出接口将数据输出到数据处理单元。

所述数据处理单元读取数据采集单元的数据,输入到中央处理器进行处理,包括预处理模块、主钟驾驭量生成模块、备钟驾驭量生成模块、故障检测模块。预处理模块将数据进行粗差剔除,滤波等预处理;主钟驾驭量生成模块生成主钟驾驭量;备钟驾驭量生成模块生成备钟驾驭量;故障检测模块检测原子钟异常情况。数据处理单元将处理结果发送到控制与显示单元。

所述控制与显示单元包括阵列键盘及配置模块、液晶屏及显示控制模块和时间保持控制模块。配置模块接收阵列键盘输入配置相关参数信息;液晶屏及显示控制模块通过显示屏显示主备钟差图,显示原子钟故障信息;时间保持控制模块向主备钟的相位微调仪发送驾驭控制量,主钟故障时向切换开关发送切换指令,向锁相环电路发送保持指令。

所述输出时间频率信号保持单元包括功率合成模块、锁相环电路。功率合成模块将主钟和备钟并行连接,得到一路综合输出信号,作为后置的锁相环的输入;锁相环能够锁定到输入信号,具有采样电压存储控制功能,其输出作为主钟信号保持器的输出信号。

参照图1,本发明的实施例包括数据采集单元、数据处理单元、显示与控制单元、输出时间频率信号保持单元。数据采集单元采集主备钟差、主钟与第三方钟钟差、备钟与第三方钟钟差,通过网络获得钟组比对数据;数据处理单元对数据进行预处理,计算主钟驾驭量,备钟驾驭量,检测原子钟异常情况;控制与显示单元根据数据处理单元的结果向主备钟的相位微调仪发送驾驭控制量,主钟故障时向切换开关发送切换指令,向锁相环电路发送保持指令,通过显示屏显示主备钟差图,显示原子钟故障信息;输出频率信号保持单元通过功合器将主钟和备钟并行连接,将功合器的输出作为后置的具有采样电压存储控制功能的锁相环的输入,并将锁相环的输出作为主钟信号保持器的输出信号。

参照图2,本发明的数据采集单元包括多通道相位比较电路、数据存储模块以及网络数据读取接口,数据输出接口。多通道相位比较电路基于双混频时差测量原理,用于主备钟差、主钟与第三方钟钟差以及备钟与第三方钟钟差的测量,测量数据存储在存储模块中;通过网络接口读取钟组比对数据,放置于存储模块;所有数据输出到数据处理单元。

参照图3,本发明的数据处理单元读取数据采集单元的数据,输入到中央处理器进行处理,包括预处理模块、主钟驾驭量生成模块、备钟驾驭量生成模块、故障检测模块。预处理模块将数据进行粗差剔除,滤波等预处理;主钟驾驭量生成模块生成主钟驾驭量;备钟驾驭量生成模块生成备钟驾驭量;故障检测模块检测原子钟异常情况。数据处理单元将处理结果发送到控制与显示单元。

参照图4,本发明的控制与显示单元包括阵列键盘及配置模块、液晶屏及显示控制模块和时间保持控制模块。其中,阵列键盘包括4×3的数字键盘和2×3的功能键盘,主要用于配置参数的输入;液晶显示屏采用192×64,主要用于主备钟差和故障信息的显示;配置模块和显示控制模块采用ARM LPC3214实现,主要用于对键盘输入的配置参数转换成系统容易识别和处理的二进制数据,同时实现对液晶显示屏的控制。配置模块接收阵列键盘输入配置相关参数信息;液晶屏及显示控制模块通过显示屏显示主备钟差图,显示原子钟故障信息;时间保持控制模块向主备钟的相位微调仪发送驾驭控制量,主钟故障时向切换开关发送切换指令,向锁相环电路发送保持指令。

参照图5,本发明中的输出时间频率信号保持单元包括功率合成模块、锁相环电路。功率合成模块将主钟和备钟并行连接,得到一路综合输出信号,作为后置的锁相环的输入;基于FPGA实现的锁相保持模块,包括信号整形、锁相和单片机控制。

选择MOTOROLA公司的三线接收器(Triple Line Receiver)MC10116来实现信号的整形。但是整形后的信号为ECL电平,而非FPGA所能处理的TTL电平,所以我们采用SN65LVELT23进行ECL转TTL电平。

FPGA内部主要实现两路参考信号与外部高精度VCXO信号的鉴相,放大并产生一个鉴相脉宽信号,经由外部电路转换生成电压信号送入ADC去采样。同时在前期会使用内部锁相环来产生一个高频信号与参考信号去比对,通过测频的方式会先对晶振先进行同步,便于后面锁相精度的提高。单片机主要处理鉴相电压信号,通过算法处理来操作DAC来控制VCXO的压控端。此次DAC使用两路,一路16-bit,一路12-bit,通过选择合适的权重来控制晶振,实现粗调和细调,可对晶振达到精确控制。

单片机的主要作用是控制FPGA来进行测频、鉴相等;通过合理的算法来切换两路信号,并使DA输出一个合理的值来保持晶振输出。

守时系统主钟信号保持器专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0