专利摘要

本发明公开了一种基于CNFET的三值加法计数器,包括脉冲信号发生器、n个加法记数单元和n输入与门,脉冲信号发生器具有输入端和输出端,加法记数单元具有输入端、输出端、时钟控制端和进位输出端,n输入与门具有n个输入端和输出端,脉冲信号发生器的输出端分别与n个加法记数单元的时钟控制端连接,n个加法记数单元的进位端与n输入与门的n个输入端一一对应连接,n输入与门的输出端为三值加法记数器的进位输出端,第k个加法记数单元的进位输出端和第k+1个加法记数单元的输入端连接,k=1,2,…,n‑1,第j个加法记数单元的输出端为三值加法计数器的第j位输出端,j=1,2,…,n;优点是减少了无效操作,降低了电路功耗与延时,具有高速低功耗特性。

权利要求

1.一种基于CNFET的三值加法计数器,其特征在于包括脉冲信号发生器、n个加法记数单元和n输入与门,其中n为大于等于1的整数,所述的脉冲信号发生器具有输入端和输出端,所述的加法记数单元具有输入端、输出端、时钟控制端和进位输出端,所述的n输入与门具有n个输入端和输出端;

所述的脉冲信号发生器的输出端分别与n个所述的加法记数单元的时钟控制端连接,n个所述的加法记数单元的进位端与所述的n输入与门的n个输入端一一对应连接,所述的n输入与门的输出端为所述的三值加法记数器的进位输出端,第1个所述的加法记数单元的输入端为所述的三值加法计数器的输入端,第k个所述的加法记数单元的进位输出端和第k+1个所述的加法记数单元的输入端连接,k=1,2,…,n-1,第j个所述的加法记数单元的输出端为所述的三值加法计数器的第j位输出端,j=1,2,…,n;

所述的脉冲信号发生器包括第一反相器、第二反相器、第一CNFET管、第二CNFET管和第三CNFET管,所述的第一CNFET管为P型CNFET管,所述的第二CNFET管和所述的第三CNFET管为N型CNFET管,所述的第一反相器的输入端、所述的第一CNFET管的源极和所述的第二CNFET管的栅极连接且其连接端为所述的脉冲信号发生器的输入端,所述的第一反相器的输出端、所述的第一CNFET管的栅极和所述的第三CNFET管的栅极连接,所述的第一CNFET管的漏极、所述的第二CNFET管的漏极和所述的第二反相器的输入端连接,所述的第二CNFET管的源极和所述的第三CNFET管的漏极连接,所述的第三CNFET管的源极接地,所述的第二反相器的输出端为所述的脉冲信号发生器的输出端;

所述的加法记数单元包括T触发器和进位电路,所述的T触发器具有时钟控制端、输入端和输出端,所述的进位电路具有输入端和输出端,所述的T触发器的时钟控制端为所述的加法记数单元的时钟控制端,所述的T触发器的输入端为所述的加法记数单元的输入端,所述的T触发器的输出端和所述的进位电路的输入端连接且其连接端为所述的加法记数单元的输出端,所述的进位电路的输出端为所述的加法记数单元的进位输出端,所述的T触发器包括一个NTI门电路、四个PTI门电路、第四CNFET管、第五CNFET管、第六CNFET管、第七CNFET管、第八CNFET管、第九CNFET管、第十CNFET管、第十一CNFET管、第十二CNFET管、第十三CNFET管、第十四CNFET管、第十五CNFET管、第十六CNFET管、第十七CNFET管、第十八CNFET管、第十九CNFET管和第二十CNFET管,所述的NTI门电路具有输入端和输出端,所述的PTI门电路具有输入端和输出端,四个所述的PTI门电路分别为第一PTI门电路、第二PTI门电路、第三PTI门电路和第四PTI门电路,所述的第四CNFET管、所述的第十CNFET管、所述的第十五CNFET管和所述的第二十CNFET管为P型CNFET管,所述的第五CNFET管、所述的第六CNFET管、所述的第七CNFET管、所述的第八CNFET管、所述的第九CNFET管、所述的第十一CNFET管、所述的第十二CNFET管、所述的第十三CNFET管、所述的第十四CNFET管、所述的第十六CNFET管、所述的第十七CNFET管、所述的第十八CNFET管和所述的第十九CNFET管为N型CNFET管,所述的第四CNFET管的源极、所述的第十CNFET管的源极和所述的第十五CNFET管的源极连接且其连接端接入第一电源,所述的第二十CNFET管的源极接入第二电源,所述的第二电源为所述的第一电源的一半,所述的四CNFET管的栅极、所述的第九CNFET管的栅极、所述的第十四CNFET管的栅极、所述的第十五CNFET管的栅极和所述的第十九CNFET管的栅极连接且其连接端为所述的T触发器的时钟控制端,所述的第四CNFET管的漏极、所述的第五CNFET管的漏极和所述的第十CNFET管的栅极连接,所述的第五CNFET管的源极和所述的第六CNFET管的漏极连接,所述的第五CNFET管的栅极、所述的第一PTI门电路的输入端、所述的第十一CNFET管的栅极、所述的第三PTI门电路的输入端、所述的第十六CNFET管的栅极和所述的第四PTI门电路的输入端连接且其连接端为所述的T触发器的输入端,所述的第六CNFET管的源极和所述的第七CNFET管的漏极连接,所述的第六CNFET管的栅极和所述的第一PTI门电路的输出端连接,所述的第七CNFET管的源极和所述的第八CNFET管的漏极连接,所述的第七CNFET管的栅极和所述的第二PTI门电路的输出端连接,所述的第八CNFET管的源极和所述的第九CNFET管的漏极连接,所述的第八CNFET管的栅极、所述的第二PTI门电路的输入端、所述的第十CNFET管的漏极、所述的第十一CNFET管的漏极、所述的第十三CNFET管的栅极、所述的第二十CNFET管的漏极和所述的NTI门电路的输入端连接且其连接端为所述的T触发器的输出端,所述的第九CNFET管的源极、所述的第十四CNFET管的源极和所述的第十九CNFET管的源极接地,所述的第十一CNFET管的源极和所述的第十二CNFET管的漏极连接,所述的第十二CNFET管的源极和所述的第十三CNFET管的漏极连接,所述的第十二CNFET管的栅极和所述的第三PTI门电路的输出端连接,所述的第十三CNFET管的源极和所述的第十四CNFET管的漏极连接,所述的第十五CNFET管的漏极、所述的第十六CNFET管的漏极和所述的第二十CNFET管的栅极连接,所述的第十六CNFET管的源极和所述的第十七CNFET管的漏极连接,所述的第十七CNFET管的源极和所述的第十八CNFET管的漏极连接,所述的第十七CNFET管的栅极和所述的第四PTI门电路的输出端连接,所述的第十八CNFET管的源极和所述的第十九CNFET管的漏极连接,所述的第十八CNFET管的栅极和所述的NTI门电路的输出端连接。

2.根据权利要求1所述的一种基于CNFET的三值加法计数器,其特征在于所述的NTI门电路包括第二十一CNFET管和第二十二CNFET管,所述的第二十一CNFET管为P型CNFET管,所述的第二十二CNFET管为N型CNFET管,所述的第二十一CNFET管的源极接入所述的第一电源,所述的第二十一CNFET管的栅极和所述的第二十二CNFET管的栅极连接且其连接端为所述的NTI门电路的输入端,所述的第二十二CNFET管的源极接地,所述的第二十一CNFET管的漏极和所述的第二十二CNFET管的漏极连接且其连接端为所述的NTI门电路的输出端。

3.根据权利要求2所述的一种基于CNFET的三值加法计数器,其特征在于所述的第二十一CNFET管的管径为0.626nm,所述的第二十二CNFET管的管径为2.505nm。

4.根据权利要求1所述的一种基于CNFET的三值加法计数器,其特征在于所述的PTI门电路包括第二十三CNFET管和第二十四CNFET管,所述的第二十三CNFET管为P型CNFET管,所述的第二十四CNFET管为N型CNFET管,所述的第二十三CNFET管的源极接入所述的第一电源,所述的第二十三CNFET管的栅极和所述的第二十四CNFET管的栅极连接且其连接端为所述的PTI门电路的输入端,所述的第二十四CNFET管的源极接地,所述的第二十三CNFET管的漏极和所述的第二十四CNFET管的漏极连接且其连接端为所述的PTI门电路的输出端。

5.根据权利要求4所述的一种基于CNFET的三值加法计数器,其特征在于所述的第二十三CNFET管的管径为2.505nm,所述的第二十四CNFET管的管径为0.626nm。

6.根据权利要求1所述的一种基于CNFET的三值加法计数器,其特征在于所述的进位电路包括第二十五CNFET管、第二十六CNFET管、第二十七CNFET管和第二十八CNFET管,所述的第二十五CNFET管和所述的第二十七CNFET管为P型CNFET管,所述的第二十六CNFET管和所述的第二十八CNFET管为N型CNFET管,所述的第二十五CNFET管的源极接入所述的第一电源,所述的第二十五CNFET管的漏极、所述的第二十六CNFET管的漏极、所述的第二十七CNFET管的栅极和所述的第二十八CNFET管的栅极连接,所述的第二十五CNFET管的栅极和所述的第二十六CNFET管的栅极连接且其连接端为所述的进位电路的输入端,所述的第二十六CNFET管的源极和所述的第二十八CNFET管的源极接地,所述的第二十七CNFET管的源极接入所述的第二电源,所述的第二十七CNFET管的漏极和所述的第二十八CNFET管的漏极连接且其连接端为所述的进位电路的输出端。

7.根据权利要求6所述的一种基于CNFET的三值加法计数器,其特征在于所述的第二十五CNFET管的管径为1.487nm,所述的第二十六CNFET管的管径为0.626nm,所述的第二十七CNFET管的管径为0.626nm,所述的第二十八CNFET管的管径为1.487nm。

8.根据权利要求1所述的一种基于CNFET的三值加法计数器,其特征在于所述的第一CNFET管的管径为1.487nm,所述的第二CNFET管的管径为1.487nm,所述的第三CNFET管的管径为1.487nm,所述的第四CNFET管的管径为1.088nm,所述的第五CNFET管的管径为1.088nm,所述的第六CNFET管的管径为0.903nm,所述的第七CNFET管的管径为0.903nm,所述的第八CNFET管的管径为1.088nm,所述的第九CNFET管的管径为0.795nm,所述的第十CNFET管的管径为1.088nm,所述的第十一CNFET管的管径为1.088nm,所述的第十二CNFET管的管径为0.903nm,所述的第十三CNFET管的管径为0.795nm,所述的第十四CNFET管的管径为0.795nm,所述的第十五CNFET管的管径为1.088nm,所述的第十六CNFET管的管径为1.088nm,所述的第十七CNFET管的管径为0.903nm,所述的第十八CNFET管的管径为0.903nm,所述的第十九CNFET管的管径为0.795nm,所述的第二十CNFET管的管径为2.505nm。

9.根据权利要求1~8中任一项所述的一种基于CNFET的三值加法计数器,其特征在于所述的第一电源为0.9V,所述的第二电源为0.45V。

10.根据权利要求1所述的一种基于CNFET的三值加法计数器,其特征在于所述的第一反相器包括第二十九CNFET管和第三十CNFET管,所述的第二十九CNFET管为P型CNFET管,所述的第三十CNFET管为N型CNFET管,所述的第二十九CNFET管的管径为1.096nm,所述的第三十CNFET管的管径为1.096nm,所述的第二十九CNFET管的源极接入所述的第一电源,所述的第二十九CNFET管的栅极和所述的第三十CNFET管的栅极连接且其连接端为所述的第一反相器的输入端,所述的第二十九CNFET管的漏极和所述的第三十CNFET管的漏极连接且其连接端为所述的第一反相器的输出端,所述的第三十CNFET管的源极接地,所述的第二反相器的电路结构和所述的第一反相器相同。

说明书

技术领域

本发明涉及一种三值加法计数器,尤其是涉及一种基于CNFET的三值加法计数器。

背景技术

随着CMOS工艺和集成电路技术的发展,电路的微型化给人们的生活带来极大的方便,同时对高集成度和低功耗等特性提出更高的要求。特别是高集成度问题,由于特征尺寸缩小使得单位芯片面积上集成的元件数目急剧增加,集成电路的特征尺寸已经进入纳米量级。在超大规模集成电路(Very Large Scale Integration,VLSI)中,有70%以上的硅片面积用于布线,进一步制约集成度的提高。在纳米量级下,互连线寄生效应带来的门延时、互连线串扰、功耗增加等问题变得更加严重。多值逻辑(Multi-Valued Logic,MVL)电路的特性为解决这些问题提供了新的途径。多值逻辑突破了传统二值逻辑信号取值“0”、“1”的限制,如多值逻辑最小基的三值逻辑,其信号可取值“0”、“1”和“2”,因此多值逻辑电路单线信息携带量高,空间或时间利用率充分,有效的降低芯片的布线面积,提高电路的集成度。

碳纳米场效应晶体管(CNFET,Carbon Nanotube Field Effect Transistor)是一种新型的低功耗高性能器件,它具有良好的电学和化学特性。CNFET凭借近似弹道传输特性,使得电子可以在直径为1-2nm的管内传输,从而突破CMOS工艺限制。此外弹道传输提升了传输效率,因此碳纳米管构成的场效应晶体管具有高速低功耗特性,将CNFET应用到低功耗集成电路芯片中,不仅能增强器件的性能,而且还丰富了微小面积芯片的有效功能。

计数器是现代计算机ALU中最基础的部件,具有脉冲计数、分频、定时、产生节拍脉冲以及数字运算等功能。三值计数器可以传输“0”,“1”,“2”三种信号,因此每一个线路的信息传输量是二值电路的1.5倍。

鉴此,设计一种高速低功耗的基于CNFET的三值加法计数器,对于提高加法计数器的性能具有重要意义。

发明内容

本发明所要解决的技术问题是提供一种在保证具有正确的逻辑功能的基础上,高速低功耗的基于CNFET的三值加法计数器。

本发明解决上述技术问题所采用的技术方案为:一种基于CNFET的三值加法计数器,包括脉冲信号发生器、n个加法记数单元和n输入与门,其中n为大于等于1的整数,所述的脉冲信号发生器具有输入端和输出端,所述的加法记数单元具有输入端、输出端、时钟控制端和进位输出端,所述的n输入与门具有n个输入端和输出端;所述的脉冲信号发生器的输出端分别与n个所述的加法记数单元的时钟控制端连接,n个所述的加法记数单元的进位端与所述的n输入与门的n个输入端一一对应连接,所述的n输入与门的输出端为所述的三值加法记数器的进位输出端,第1个所述的加法记数单元的输入端为所述的三值加法计数器的输入端,第k个所述的加法记数单元的进位输出端和第k+1个所述的加法记数单元的输入端连接,k=1,2,…,n-1,第j个所述的加法记数单元的输出端为所述的三值加法计数器的第j位输出端,j=1,2,…,n;所述的脉冲信号发生器包括第一反相器、第二反相器、第一CNFET管、第二CNFET管和第三CNFET管,所述的第一CNFET管为P型CNFET管,所述的第二CNFET管和所述的第三CNFET管为N型CNFET管,所述的第一反相器的输入端、所述的第一CNFET管的源极和所述的第二CNFET管的栅极连接且其连接端为所述的脉冲信号发生器的输入端,所述的第一反相器的输出端、所述的第一CNFET管的栅极和所述的第三CNFET管的栅极连接,所述的第一CNFET管的漏极、所述的第二CNFET管的漏极和所述的第二反相器的输入端连接,所述的第二CNFET管的源极和所述的第三CNFET管的漏极连接,所述的第三CNFET管的源极接地,所述的第二反相器的输出端为所述的脉冲信号发生器的输出端;所述的加法记数单元包括T触发器和进位电路,所述的T触发器具有时钟控制端、输入端和输出端,所述的进位电路具有输入端和输出端,所述的T触发器的时钟控制端为所述的加法记数单元的时钟控制端,所述的T触发器的输入端为所述的加法记数单元的输入端,所述的T触发器的输出端和所述的进位电路的输入端连接且其连接端为所述的加法记数单元的输出端,所述的进位电路的输出端为所述的加法记数单元的进位输出端,所述的T触发器包括一个NTI门电路、四个PTI门电路、第四CNFET管、第五CNFET管、第六CNFET管、第七CNFET管、第八CNFET管、第九CNFET管、 第十CNFET管、第十一CNFET管、第十二CNFET管、第十三CNFET管、第十四CNFET管、第十五CNFET管、第十六CNFET管、第十七CNFET管、第十八CNFET管、第十九CNFET管和第二十CNFET管,所述的NTI门电路具有输入端和输出端,所述的PTI门电路具有输入端和输出端,四个所述的PTI门电路分别为第一PTI门电路、第二PTI门电路、第三PTI门电路和第四PTI门电路,所述的第四CNFET管、所述的第十CNFET管、所述的第十五CNFET管和所述的第二十CNFET管为P型CNFET管,所述的第五CNFET管、所述的第六CNFET管、所述的第七CNFET管、所述的第八CNFET管、所述的第九CNFET管、所述的第十一CNFET管、所述的第十二CNFET管、所述的第十三CNFET管、所述的第十四CNFET管、所述的第十六CNFET管、所述的第十七CNFET管、所述的第十八CNFET管和所述的第十九CNFET管为N型CNFET管,所述的第四CNFET管的源极、所述的第十CNFET管的源极和所述的第十五CNFET管的源极连接且其连接端接入第一电源,所述的第二十CNFET管的源极接入第二电源,所述的第二电源为所述的第一电源的一半,所述的第四CNFET管的栅极、所述的第九CNFET管的栅极、所述的第十四CNFET管的栅极、所述的第十五CNFET管的栅极和所述的第十九CNFET管的栅极连接且其连接端为所述的T触发器的时钟控制端,所述的第四CNFET管的漏极、所述的第五CNFET管的漏极和所述的第十CNFET管的栅极连接,所述的第五CNFET管的源极和所述的第六CNFET管的漏极连接,所述的第五CNFET管的栅极、所述的第一PTI门电路的输入端、所述的第十一CNFET管的栅极、所述的第三PTI门电路的输入端、所述的第十六CNFET管的栅极和所述的第四PTI门电路的输入端连接且其连接端为所述的T触发器的输入端,所述的第六CNFET管的源极和所述的第七CNFET管的漏极连接,所述的第六CNFET管的栅极和所述的第一PTI门电路的输出端连接,所述的第七CNFET管的源极和所述的第八CNFET管的漏极连接,所述的第七CNFET管的栅极和所述的第二PTI门电路的输出端连接,所述的第八CNFET管的源极和所述的第九CNFET管的漏极连接,所述的第八CNFET管的栅极、所述的第二PTI门电路的输入端、所述的第十CNFET管的漏极、所述的第十一CNFET管的漏极、所述的第十三CNFET管的栅极、所述的第二十CNFET管的漏极和所述的NTI门电路的输入端连接且其连接端为所述的T触发器的输出端,所述的第九CNFET管的源极、所述的第十四CNFET管的源极和所述的第十九CNFET管的源极接地,所述的第十一CNFET管的源极和所述的第十二CNFET管的漏极连接,所述的第十二CNFET管的源极和所述的第十三CNFET管的漏极连接,所述的第十二 CNFET管的栅极和所述的第三PTI门电路的输出端连接,所述的第十三CNFET管的源极和所述的第十四CNFET管的漏极连接,所述的第十五CNFET管的漏极、所述的第十六CNFET管的漏极和所述的第二十CNFET管的栅极连接,所述的第十六CNFET管的源极和所述的第十七CNFET管的漏极连接,所述的第十七CNFET管的源极和所述的第十八CNFET管的漏极连接,所述的第十七CNFET管的栅极和所述的第四PTI门电路的输出端连接,所述的第十八CNFET管的源极和所述的第十九CNFET管的漏极连接,所述的第十八CNFET管的栅极和所述的NTI门电路的输出端连接。

所述的NTI门电路包括第二十一CNFET管和第二十二CNFET管,所述的第二十一CNFET管为P型CNFET管,所述的第二十二CNFET管为N型CNFET管,所述的第二十一CNFET管的源极接入所述的第一电源,所述的第二十一CNFET管的栅极和所述的第二十二CNFET管的栅极连接且其连接端为所述的NTI门电路的输入端,所述的第二十二CNFET管的源极接地,所述的第二十一CNFET管的漏极和所述的第二十二CNFET管的漏极连接且其连接端为所述的NTI门电路的输出端。

所述的第二十一CNFET管的管径为0.626nm,所述的第二十二CNFET管的管径为2.505nm。

所述的PTI门电路包括第二十三CNFET管和第二十四CNFET管,所述的第二十三CNFET管为P型CNFET管,所述的第二十四CNFET管为N型CNFET管,所述的第二十三CNFET管的源极接入所述的第一电源,所述的第二十三CNFET管的栅极和所述的第二十四CNFET管的栅极连接且其连接端为所述的PTI门电路的输入端,所述的第二十四CNFET管的源极接地,所述的第二十三CNFET管的漏极和所述的第二十四CNFET管的漏极连接且其连接端为所述的PTI门电路的输出端。

所述的第二十三CNFET管的管径为2.505nm,所述的第二十四CNFET管的管径为0.626nm。

所述的进位电路包括第二十五CNFET管、第二十六CNFET管、第二十七CNFET管和第二十八CNFET管,所述的第二十五CNFET管和所述的第二十七CNFET管为P型CNFET管,所述的第二十六CNFET管和所述的第二十八CNFET管为N型CNFET管,所述的第二十五CNFET管的源极接入所述的第一电源,所述的第二十五CNFET管的漏极、所述的第二十六CNFET管的漏极、所述的第二十七CNFET管的栅极和所述的第二十八CNFET管的栅极连接,所述的第二十五CNFET管的栅极和所述的第二十六CNFET管的栅极连接且其连接端为所述的进位电路的输入端,所述的第二十六 CNFET管的源极和所述的第二十八CNFET管的源极接地,所述的第二十七CNFET管的源极接入所述的第二电源,所述的第二十七CNFET管的漏极和所述的第二十八CNFET管的漏极连接且其连接端为所述的进位电路的输出端。

所述的第二十五CNFET管的管径为1.487nm,所述的第二十六CNFET管的管径为0.626nm,所述的第二十七CNFET管的管径为0.626nm,所述的第二十八CNFET管的管径为1.487nm。

所述的第一CNFET管的管径为1.487nm,所述的第二CNFET管的管径为1.487nm,所述的第三CNFET管的管径为1.487nm,所述的第四CNFET管的管径为1.088nm,所述的第五CNFET管的管径为1.088nm,所述的第六CNFET管的管径为0.903nm,所述的第七CNFET管的管径为0.903nm,所述的第八CNFET管的管径为1.088nm,所述的第九CNFET管的管径为0.795nm,所述的第十CNFET管的管径为1.088nm,所述的第十一CNFET管的管径为1.088nm,所述的第十二CNFET管的管径为0.903nm,所述的第十三CNFET管的管径为0.795nm,所述的第十四CNFET管的管径为0.795nm,所述的第十五CNFET管的管径为1.088nm,所述的第十六CNFET管的管径为1.088nm,所述的第十七CNFET管的管径为0.903nm,所述的第十八CNFET管的管径为0.903nm,所述的第十九CNFET管的管径为0.795nm,所述的第二十CNFET管的管径为2.505nm。

所述的第一电源为0.9V,所述的第二电源为0.45V。

所述的第一反相器包括第二十九CNFET管和第三十CNFET管,所述的第二十九CNFET管为P型CNFET管,所述的第三十CNFET管为N型CNFET管,所述的第二十九CNFET管的管径为1.096nm,所述的第三十CNFET管的管径为1.096nm,所述的第二十九CNFET管的源极接入所述的第一电源,所述的第二十九CNFET管的栅极和所述的第三十CNFET管的栅极连接且其连接端为所述的第一反相器的输入端,所述的第二十九CNFET管的漏极和所述的第三十CNFET管的漏极连接且其连接端为所述的第一反相器的输出端,所述的第三十CNFET管的源极接地,所述的第二反相器的电路结构和所述的第一反相器相同。

与现有技术相比,本发明的优点在于通过脉冲信号发生器、n个加法记数单元和n输入与门构建基于CNFET的三值加法计数器,其中n为大于等于1的整数,脉冲信号发生器具有输入端和输出端,加法记数单元具有输入端、输出端、时钟控制端和进位输出端,n输入与门具有n个输入端和输出端,脉冲信号发生器的输出端分别与n个加法记数单元的时钟控制端连接,n个加法记数单元的进位端与n输入与门的n个输入端一 一对应连接,n输入与门的输出端为三值加法记数器的进位输出端,第1个加法记数单元的输入端为三值加法计数器的输入端,第k个加法记数单元的进位输出端和第k+1个加法记数单元的输入端连接,k=1,2,…,n-1,第j个加法记数单元的输出端为三值加法计数器的第j位输出端,j=1,2,…,n;脉冲信号发生器包括第一反相器、第二反相器、第一CNFET管、第二CNFET管和第三CNFET管,加法记数单元包括T触发器和进位电路,T触发器具有时钟控制端、输入端和输出端,进位电路具有输入端和输出端,T触发器的时钟控制端为加法记数单元的时钟控制端,T触发器的输入端为加法记数单元的输入端,T触发器的输出端和进位电路的输入端连接且其连接端为加法记数单元的输出端,进位电路的输出端为加法记数单元的进位输出端,T触发器包括一个NTI门电路、四个PTI门电路、第四CNFET管、第五CNFET管、第六CNFET管、第七CNFET管、第八CNFET管、第九CNFET管、第十CNFET管、第十一CNFET管、第十二CNFET管、第十三CNFET管、第十四CNFET管、第十五CNFET管、第十六CNFET管、第十七CNFET管、第十八CNFET管、第十九CNFET管和第二十CNFET管;当三值加法计数器的输入端接入信号“1”时,脉冲信号发生器的输出端每输出一个脉冲控制信号clkp,每个加法记数单元中的T触发器的输出信号Q会跳变一次;若Q=0,则第十六CNFET管、第十七CNFET管、第十八CNFET管和第十九CNFET管构成的右侧支路导通,第十五CNFET管的漏极、第十六CNFET管的漏极和第二十CNFET管的栅极的连接节点Z处的电压下拉为0,T触发器的输出端输出信号“1”;若Q=1,则第五CNFET管、第六CNFET管、第七CNFET管、第八CNFET管和第九CNFET管构成的左侧支路导通,第四CNFET管的漏极、第五CNFET管的漏极和第十CNFET管的栅极的连接节点Y处的电压下拉为0,T触发器的输出端输出信号“2”;若Q=2,则第十一CNFET管、第十二CNFET管、第十三CNFET管和第十四CNFET管构成的中间支路导通,T触发器的输出端输出信号“0”;当T=0时或者clkp为低电平时,右侧支路、左侧支路和中间支路均不导通,Q维持上一状态不变,由此每个加法记数单元中的T触发器均精简了T=0电路,简化了电路,有效的减少了无效操作,极大的降低了电路功耗与延时,具有高速低功耗特性,采用CNFET管来设计本发明的基于CNFET的三值加法计数器,克服了CMOS工艺极限的问题,对进一步研究更大规模的低功耗三值时序电路具有重要意义,利用HSPICE对本发明的基于CNFET的三值加法计数器进行逻辑功能和能耗的模拟分析,实验证明本发明的基于CNFET的三值加法计数器实现了完整的三值计数器功能,逻辑功能正确,低功耗特性明显。

附图说明

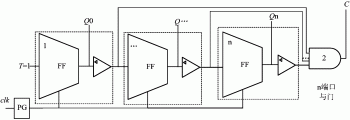

图1为本发明的基于CNFET的三值加法计数器的结构图;

图2(a)为本发明的基于CNFET的三值加法计数器的脉冲信号发生器的电路图;

图2(b)为本发明的基于CNFET的三值加法计数器的脉冲信号发生器的符号图;

图3(a)为本发明的基于CNFET的三值加法计数器的T触发器的电路图;

图3(b)为本发明的基于CNFET的三值加法计数器的T触发器的符号图;

图4(a)为本发明的基于CNFET的三值加法计数器的NTI门电路的电路图;

图4(b)为本发明的基于CNFET的三值加法计数器的NTI门电路的符号图;

图5(a)为本发明的基于CNFET的三值加法计数器的PTI门电路的电路图;

图5(b)为本发明的基于CNFET的三值加法计数器的PTI门电路的符号图;

图6(a)为本发明的基于CNFET的三值加法计数器的进位电路的电路图;

图6(b)为本发明的基于CNFET的三值加法计数器的进位电路的符号图;

图7(a)为本发明的基于CNFET的三值加法计数器的第一反相器的电路图;

图7(b)为本发明的基于CNFET的三值加法计数器的第一反相器的符号图;

图8为本发明的基于CNFET的三值加法计数器的仿真波形图;

图9为本发明的基于CNFET的三值加法计数器和T触发器的能耗图。

具体实施方式

以下结合附图实施例对本发明作进一步详细描述。

实施例一:如图1、图2(a)、图2(b)、图3(a)和图3(b)所示,一种基于CNFET的三值加法计数器,包括脉冲信号发生器、n个加法记数单元和n输入与门,其中n为大于等于1的整数,脉冲信号发生器具有输入端和输出端,加法记数单元具有输入端、输出端、时钟控制端和进位输出端,n输入与门具有n个输入端和输出端;脉冲信号发生器的输出端分别与n个加法记数单元的时钟控制端连接,n个加法记数单元的进位端与n输入与门的n个输入端一一对应连接,n输入与门的输出端为三值加法记数器的进位输出端,第1个加法记数单元的输入端为三值加法计数器的输入端,第k个加法记数单元的进位输出端和第k+1个加法记数单元的输入端连接,k=1,2,…,n-1,第j个加 法记数单元的输出端为三值加法计数器的第j位输出端,j=1,2,…,n;脉冲信号发生器包括第一反相器、第二反相器、第一CNFET管N1、第二CNFET管N2和第三CNFET管N3,第一CNFET管N1为P型CNFET管,第二CNFET管N2和第三CNFET管N3为N型CNFET管,第一反相器的输入端、第一CNFET管N1的源极和第二CNFET管N2的栅极连接且其连接端为脉冲信号发生器的输入端,第一反相器的输出端、第一CNFET管N1的栅极和第三CNFET管N3的栅极连接,第一CNFET管N1的漏极、第二CNFET管N2的漏极和第二反相器的输入端连接,第二CNFET管N2的源极和第三CNFET管N3的漏极连接,第三CNFET管N3的源极接地,第二反相器的输出端为脉冲信号发生器的输出端;加法记数单元包括T触发器和进位电路,T触发器具有时钟控制端、输入端和输出端,进位电路具有输入端和输出端,T触发器的时钟控制端为加法记数单元的时钟控制端,T触发器的输入端为加法记数单元的输入端,T触发器的输出端和进位电路的输入端连接且其连接端为加法记数单元的输出端,进位电路的输出端为加法记数单元的进位输出端,T触发器包括一个NTI门电路、四个PTI门电路、第四CNFET管N4、第五CNFET管N5、第六CNFET管N6、第七CNFET管N7、第八CNFET管N8、第九CNFET管N9、第十CNFET管N10、第十一CNFET管N11、第十二CNFET管N12、第十三CNFET管N13、第十四CNFET管N14、第十五CNFET管N15、第十六CNFET管N16、第十七CNFET管N17、第十八CNFET管N18、第十九CNFET管N19和第二十CNFET管N20,NTI门电路具有输入端和输出端,PTI门电路具有输入端和输出端,四个PTI门电路分别为第一PTI门电路、第二PTI门电路、第三PTI门电路和第四PTI门电路,第四CNFET管N4、第十CNFET管N10、第十五CNFET管N15和第二十CNFET管N20为P型CNFET管,第五CNFET管N5、第六CNFET管N6、第七CNFET管N7、第八CNFET管N8、第九CNFET管N9、第十一CNFET管N11、第十二CNFET管N12、第十三CNFET管N13、第十四CNFET管N14、第十六CNFET管N16、第十七CNFET管N17、第十八CNFET管N18和第十九CNFET管N19为N型CNFET管,第四CNFET管N4的源极、第十CNFET管N10的源极和第十五CNFET管N15的源极连接且其连接端接入第一电源,第二十CNFET管N20的源极接入第二电源,第二电源为第一电源的一半,第四CNFET管N4的栅极、第九CNFET管N9的栅极、第十四CNFET管N14的栅极、第十五CNFET管N15的栅极和第十九CNFET管N19的栅极连接且其连接端为T触发器的时钟控制端,第四CNFET管N4的漏极、第五CNFET管N5的漏极和第十CNFET管N10的栅极连接,第五CNFET管N5的源极 和第六CNFET管N6的漏极连接,第五CNFET管N5的栅极、第一PTI门电路的输入端、第十一CNFET管N11的栅极、第三PTI门电路的输入端、第十六CNFET管N16的栅极和第四PTI门电路的输入端连接且其连接端为T触发器的输入端,第六CNFET管N6的源极和第七CNFET管N7的漏极连接,第六CNFET管N6的栅极和第一PTI门电路的输出端连接,第七CNFET管N7的源极和第八CNFET管N8的漏极连接,第七CNFET管N7的栅极和第二PTI门电路的输出端连接,第八CNFET管N8的源极和第九CNFET管N9的漏极连接,第八CNFET管N8的栅极、第二PTI门电路的输入端、第十CNFET管N10的漏极、第十一CNFET管N11的漏极、第十三CNFET管N13的栅极、第二十CNFET管N20的漏极和NTI门电路的输入端连接且其连接端为T触发器的输出端,第九CNFET管N9的源极、第十四CNFET管N14的源极和第十九CNFET管N19的源极接地,第十一CNFET管N11的源极和第十二CNFET管N12的漏极连接,第十二CNFET管N12的源极和第十三CNFET管N13的漏极连接,第十二CNFET管N12的栅极和第三PTI门电路的输出端连接,第十三CNFET管N13的源极和第十四CNFET管N14的漏极连接,第十五CNFET管N15的漏极、第十六CNFET管N16的漏极和第二十CNFET管N20的栅极连接,第十六CNFET管N16的源极和第十七CNFET管N17的漏极连接,第十七CNFET管N17的源极和第十八CNFET管N18的漏极连接,第十七CNFET管N17的栅极和第四PTI门电路的输出端连接,第十八CNFET管N18的源极和第十九CNFET管N19的漏极连接,第十八CNFET管N18的栅极和NTI门电路的输出端连接。

实施例二:如图1、图2(a)、图2(b)、图3(a)和图3(b)所示,一种基于CNFET的三值加法计数器,包括脉冲信号发生器、n个加法记数单元和n输入与门,其中n为大于等于1的整数,脉冲信号发生器具有输入端和输出端,加法记数单元具有输入端、输出端、时钟控制端和进位输出端,n输入与门具有n个输入端和输出端;脉冲信号发生器的输出端分别与n个加法记数单元的时钟控制端连接,n个加法记数单元的进位端与n输入与门的n个输入端一一对应连接,n输入与门的输出端为三值加法记数器的进位输出端,第1个加法记数单元的输入端为三值加法计数器的输入端,第k个加法记数单元的进位输出端和第k+1个加法记数单元的输入端连接,k=1,2,…,n-1,第j个加法记数单元的输出端为三值加法计数器的第j位输出端,j=1,2,…,n;脉冲信号发生器包括第一反相器、第二反相器、第一CNFET管N1、第二CNFET管N2和第三CNFET管N3,第一CNFET管N1为P型CNFET管,第二CNFET管N2和第三CNFET管N3 为N型CNFET管,第一反相器的输入端、第一CNFET管N1的源极和第二CNFET管N2的栅极连接且其连接端为脉冲信号发生器的输入端,第一反相器的输出端、第一CNFET管N1的栅极和第三CNFET管N3的栅极连接,第一CNFET管N1的漏极、第二CNFET管N2的漏极和第二反相器的输入端连接,第二CNFET管N2的源极和第三CNFET管N3的漏极连接,第三CNFET管N3的源极接地,第二反相器的输出端为脉冲信号发生器的输出端;加法记数单元包括T触发器和进位电路,T触发器具有时钟控制端、输入端和输出端,进位电路具有输入端和输出端,T触发器的时钟控制端为加法记数单元的时钟控制端,T触发器的输入端为加法记数单元的输入端,T触发器的输出端和进位电路的输入端连接且其连接端为加法记数单元的输出端,进位电路的输出端为加法记数单元的进位输出端,T触发器包括一个NTI门电路、四个PTI门电路、第四CNFET管N4、第五CNFET管N5、第六CNFET管N6、第七CNFET管N7、第八CNFET管N8、第九CNFET管N9、第十CNFET管N10、第十一CNFET管N11、第十二CNFET管N12、第十三CNFET管N13、第十四CNFET管N14、第十五CNFET管N15、第十六CNFET管N16、第十七CNFET管N17、第十八CNFET管N18、第十九CNFET管N19和第二十CNFET管N20,NTI门电路具有输入端和输出端,PTI门电路具有输入端和输出端,四个PTI门电路分别为第一PTI门电路、第二PTI门电路、第三PTI门电路和第四PTI门电路,第四CNFET管N4、第十CNFET管N10、第十五CNFET管N15和第二十CNFET管N20为P型CNFET管,第五CNFET管N5、第六CNFET管N6、第七CNFET管N7、第八CNFET管N8、第九CNFET管N9、第十一CNFET管N11、第十二CNFET管N12、第十三CNFET管N13、第十四CNFET管N14、第十六CNFET管N16、第十七CNFET管N17、第十八CNFET管N18和第十九CNFET管N19为N型CNFET管,第四CNFET管N4的源极、第十CNFET管N10的源极和第十五CNFET管N15的源极连接且其连接端接入第一电源,第二十CNFET管N20的源极接入第二电源,第二电源为第一电源的一半,第四CNFETN4管的栅极、第九CNFET管N9的栅极、第十四CNFET管N14的栅极、第十五CNFET管N15的栅极和第十九CNFET管N19的栅极连接且其连接端为T触发器的时钟控制端,第四CNFET管N4的漏极、第五CNFET管N5的漏极和第十CNFET管N10的栅极连接,第五CNFET管N5的源极和第六CNFET管N6的漏极连接,第五CNFET管N5的栅极、第一PTI门电路的输入端、第十一CNFET管N11的栅极、第三PTI门电路的输入端、第十六CNFET管N16的栅极和第四PTI门电路的输入端连接且其连接端为T触发器的输入端,第六CNFET管N6 的源极和第七CNFET管N7的漏极连接,第六CNFET管N6的栅极和第一PTI门电路的输出端连接,第七CNFET管N7的源极和第八CNFET管N8的漏极连接,第七CNFET管N7的栅极和第二PTI门电路的输出端连接,第八CNFET管N8的源极和第九CNFET管N9的漏极连接,第八CNFET管N8的栅极、第二PTI门电路的输入端、第十CNFET管N10的漏极、第十一CNFET管N11的漏极、第十三CNFET管N13的栅极、第二十CNFET管N20的漏极和NTI门电路的输入端连接且其连接端为T触发器的输出端,第九CNFET管N9的源极、第十四CNFET管N14的源极和第十九CNFET管N19的源极接地,第十一CNFET管N11的源极和第十二CNFET管N12的漏极连接,第十二CNFET管N12的源极和第十三CNFET管N13的漏极连接,第十二CNFET管N12的栅极和第三PTI门电路的输出端连接,第十三CNFET管N13的源极和第十四CNFET管N14的漏极连接,第十五CNFET管N15的漏极、第十六CNFET管N16的漏极和第二十CNFET管N20的栅极连接,第十六CNFET管N16的源极和第十七CNFET管N17的漏极连接,第十七CNFET管N17的源极和第十八CNFET管N18的漏极连接,第十七CNFET管N17的栅极和第四PTI门电路的输出端连接,第十八CNFET管N18的源极和第十九CNFET管N19的漏极连接,第十八CNFET管N18的栅极和NTI门电路的输出端连接。

如图4(a)和图4(b),本实施例中,NTI门电路包括第二十一CNFET管N21和第二十二CNFET管N22,第二十一CNFET管N21为P型CNFET管,第二十二CNFET管N22为N型CNFET管,第二十一CNFET管N21的源极接入第一电源,第二十一CNFET管N21的栅极和第二十二CNFET管N22的栅极连接且其连接端为NTI门电路的输入端,第二十二CNFET管N22的源极接地,第二十一CNFET管N21的漏极和第二十二CNFET管N22的漏极连接且其连接端为NTI门电路的输出端。

本实施例中,第二十一CNFET管N21的管径为0.626nm,第二十二CNFET管N22的管径为2.505nm。

如图5(a)和图5(b),本实施例中,PTI门电路包括第二十三CNFET管N23和第二十四CNFET管N24,第二十三CNFET管N23为P型CNFET管,第二十四CNFET管N24为N型CNFET管,第二十三CNFET管N23的源极接入第一电源,第二十三CNFET管N23的栅极和第二十四CNFET管N24的栅极连接且其连接端为PTI门电路的输入端,第二十四CNFET管N24的源极接地,第二十三CNFET管N23的漏极和第二十四CNFET管N24的漏极连接且其连接端为PTI门电路的输出端。

本实施例中,第二十三CNFET管N23的管径为2.505nm,第二十四CNFET管N24 的管径为0.626nm。

如图6(a)和图6(b),本实施例中,进位电路包括第二十五CNFET管N25、第二十六CNFET管N26、第二十七CNFET管N27和第二十八CNFET管N28,第二十五CNFET管N25和第二十七CNFET管N27为P型CNFET管,第二十六CNFET管N26和第二十八CNFET管N28为N型CNFET管,第二十五CNFET管N25的源极接入第一电源,第二十五CNFET管N25的漏极、第二十六CNFET管N26的漏极、第二十七CNFET管N27的栅极和第二十八CNFET管N28的栅极连接,第二十五CNFET管N25的栅极和第二十六CNFET管N26的栅极连接且其连接端为进位电路的输入端,第二十六CNFET管N26的源极和第二十八CNFET管N28的源极接地,第二十七CNFET管N27的源极接入第二电源,第二十七CNFET管N27的漏极和第二十八CNFET管N28的漏极连接且其连接端为进位电路的输出端。

本实施例中,第二十五CNFET管N25的管径为1.487nm,第二十六CNFET管N26的管径为0.626nm,第二十七CNFET管N27的管径为0.626nm,第二十八CNFET管N28的管径为1.487nm。

本实施例中,第一CNFET管N1的管径为1.487nm,第二CNFET管N2的管径为1.487nm,第三CNFET管N3的管径为1.487nm,第四CNFET管N4的管径为1.088nm,第五CNFET管N5的管径为1.088nm,第六CNFET管N6的管径为0.903nm,第七CNFET管N7的管径为0.903nm,第八CNFET管N8的管径为1.088nm,第九CNFET管N9的管径为0.795nm,第十CNFET管N10的管径为1.088nm,第十一CNFET管N11的管径为1.088nm,第十二CNFET管N12的管径为0.903nm,第十三CNFET管N13的管径为0.795nm,第十四CNFET管N14的管径为0.795nm,第十五CNFET管N15的管径为1.088nm,第十六CNFET管N16的管径为1.088nm,第十七CNFET管N17的管径为0.903nm,第十八CNFET管N18的管径为0.903nm,第十九CNFET管N19的管径为0.795nm,第二十CNFET管N20的管径为2.505nm。

本实施例中,第一电源vdd为0.9V,第二电源vmm为0.45V。

本实施例中,第一反相器F1包括第二十九CNFET管N29和第三十CNFET管N30,第二十九CNFET管N29为P型CNFET管,第三十CNFET管N30为N型CNFET管,第二十九CNFET管N29的管径为1.096nm,第三十CNFET管N30的管径为1.096nm,第二十九CNFET管N29的源极接入第一电源vdd,第二十九CNFET管N29的栅极和第三十CNFET管N30的栅极连接且其连接端为第一反相器F1的输入端,第二十九 CNFET管N29的漏极和第三十CNFET管N30的漏极连接且其连接端为第一反相器F1的输出端,第三十CNFET管N30的源极接地,第二反相器F2的电路结构和第一反相器F1相同。

本发明的基于CNFET的三值加法计数器采用32nm标准模型下的CNFET管实现,其中n=2,第一电源vdd=0.9V,第二电源vmm=0.45V,分别代表逻辑“2”和逻辑“1”,隧道区域和衬底间的耦合电容Csub=20pF/m。利用HSPICE对本发明的基于CNFET的三值加法计数器进行逻辑功能和能耗的模拟分析。其中,在f=250MHz下,本发明的基于CNFET的三值加法计数器的仿真波形图如图8所示,分析图8可知,每一个时钟控制信号clkp使得Q0跳变一次,当Q0为“2”时,向高位Q1进“1”;当Q0与Q1均为“2”时,进位信号C输出“1”,实现了完整的三值计数器功能,因此本发明的基于CNFET的三值加法计数器的逻辑功能正确。本发明的基于CNFET的三值加法计数器和T触发器的能耗图如图9所示,分析图9可知,本发明的基于CNFET的三值加法计数器和T触发器具有明显的低功耗特性。

一种基于CNFET的三值加法计数器专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0